FPGA vs. CPLD: Hauptunterschiede zwischen ihnen

October 11 2023

Anfrage

Globaler Lieferant elektronischer Komponenten AMPHEO PTY LTD: Umfangreiches Inventar für One-Stop-Shopping. Einfache Anfragen, schnelle, individuelle Lösungen und Angebote.

SCHNELLE ANFRAGE

ZUR RFQ-LISTE HINZUFÜGEN

Der Betrieb digitaler Systeme wird durch einen integrierten Schaltkreis, CPLD genannt, unterstützt. Ein FPGA hingegen ist ein integrierter Schaltkreis, der hauptsächlich dazu bestimmt ist, nach der Produktion von einem Kunden oder Entwickler modifiziert zu werden. FPGAs können bis zu 100.000 kleine Logikblöcke enthalten.

Entwicklung von Programmiergeräten

Was sind programmierbare Nur-Lese-Speicher (PROMs)?

PROMs, auch als programmierbare Nur-Lese-Speicher bekannt, sind einfach Speicher, die vom Benutzer leicht programmiert werden können, um ein bestimmtes Muster zu speichern. Dieses Muster kann eine Zustandsmaschine, einen rudimentären Algorithmus oder ein Mikroprozessorprogramm darstellen. Bestimmte PROMs haben ein einmaliges Programmierlimit. Andere PROMs können mehrmals programmiert und gelöscht werden, darunter EPROMs und EEPROMs. Jede kombinatorische Logik kann mit PROMs mit einer begrenzten Anzahl von Ein- und Ausgängen implementiert werden. Flip-Flops oder Mikroprozessoren – oder andere extern getaktete Komponenten – müssen hinzugefügt werden, um sequentielle Logik zu implementieren. PROMs neigen auch dazu, unglaublich langsam zu sein, was sie für Anwendungen, bei denen es auf Geschwindigkeit ankommt, unbrauchbar macht.Was sind programmierbare Logikarrays (PLAs)?

Die Geschwindigkeits- und Eingangsbeschränkungen von PROMs wurden durch Programmable Logic Arrays (PLAs) überwunden. In einem PLA sind viele Eingänge mit einer UND-Ebene verbunden, wo, je nachdem, wie das Teil codiert ist, verschiedene Signalkombinationen logisch UND-verknüpft werden können. Die ODER-Ebene empfängt die Ausgänge von der UND-Ebene, die dann in verschiedenen Kombinationen ODER-verknüpft werden, um die gewünschten Ausgänge zu erzeugen. An den Ein- und Ausgängen sind häufig Inverter vorhanden, um die Erzeugung logischer NICHTs zu ermöglichen. Obwohl sie nicht alle denkbaren Kombinationen wie ein PROM implementieren können, können diese Geräte viele kombinatorische Funktionen implementieren. Sie sind jedoch normalerweise schneller und verfügen über viel mehr Eingänge.Was ist programmierbare Array-Logik (PALs)?

Das PLA hat eine Variante namens Programmable Array Logic (PAL). Es hat eine große, programmierbare UND-Ebene zum UND-Verknüpfen von Eingängen, genau wie das PLA. Die Anzahl der Terme, die mit ODER verknüpft werden können, ist jedoch durch die feste Natur der ODER-Ebene beschränkt. Zu den Ein- und Ausgängen werden Verriegelungsvorrichtungen, exklusive ODER-Verknüpfungen, Multiplexer und andere grundlegende Logikkomponenten hinzugefügt. Die Einbeziehung zeitgesteuerter Komponenten – normalerweise Flipflops – ist entscheidend. Mit diesen Geräten kann nun eine breite Palette logischer Operationen implementiert werden, einschließlich getakteter sequentieller Logik ohne die Notwendigkeit von Zustandsmaschinen. Dies war ein bedeutender Fortschritt, der es PALs ermöglichte, in vielen Designs weitgehend die Rolle der gewöhnlichen Logik zu übernehmen. PALs sind außerdem sehr schnell.Was ist CPLD?

Was komplexe programmierbare Logikbausteine (CPLDs) zu sein versprechen, ist genau das, was sie sind. Im Wesentlichen sind sie so gestaltet, dass sie einer großen Anzahl von PALs ähneln, die auf einem einzigen Chip integriert und über einen Koppelpunktschalter miteinander verbunden sind. Sie basieren auf derselben Technologie, verwenden dieselben Programmierer und Entwicklungstools und können ein größeres Volumen und eine größere Komplexität an Schlussfolgerungen bewältigen. Das CPLD (Complex Programmable Logic Device), dessen Komplexität der von SPLD (Simple Programmable Logic Device) und FPGA entspricht, erbt die Fähigkeiten beider Geräte. CPLDs sind zwar weniger komplex als FPGAs, aber komplexer als SPLDs. PAL (Programmable Array Logic), PLA (Programmable Logic Array) und GAL sind die beliebtesten SPLDs (Generic Array Logic).Was ist FPGA?

Die anpassbare Logikblockmatrix (CLB) im Zentrum von Field Programmable Gate Arrays (FPGAs), einem Halbleiterbauelement, ist durch programmierbare Verbindungen gekoppelt. FPGAs können nach der Produktion neu programmiert werden, um bestimmten Anwendungs- oder Funktionsanforderungen gerecht zu werden. Diese Eigenschaft unterscheidet FPGAs von anwendungsspezifischen integrierten Schaltkreisen (ASICs), die speziell für bestimmte Designanforderungen erstellt werden. Obwohl einmalig programmierbare (OTP) FPGAs verfügbar sind, sind SRAM-basierte FPGAs, die bei Designänderungen aktualisiert werden können, weiter verbreitet. Anstatt eine Struktur zu haben, die der eines PAL oder eines anderen programmierbaren Bauelements ähnelt, sind Field Programmable Gate Arrays sehr ähnlich wie Gate-Array-ASICs aufgebaut. Aus diesem Grund eignen sich FPGAs hervorragend für den Einsatz in ASIC-Prototypen und anderen Anwendungen, in denen letztendlich ein ASIC implementiert wird.Video zu CPLD und FPGA

Die Grundstruktur von CPLD

CPLD-Architektur

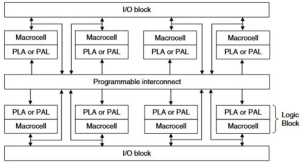

Als Weiterentwicklung von PAL besteht CPLD aus mehreren PAL-Strukturen, die als Makrozellen bezeichnet werden. Jede Makrozelle im CPLD-Paket hat Zugriff auf jeden Eingangspin, während jede Makrozelle einen bestimmten Ausgangspin hat. Die folgende Grafik zeigt das Blockdiagramm eines CPLD.

CPLD-Struktur

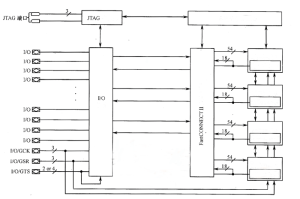

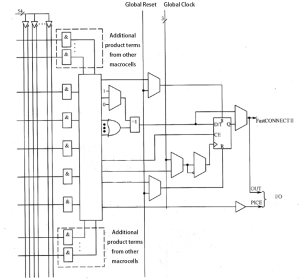

Die Struktur von CPLD basiert auf dem Produktterm (Product-Term), und die grundlegende Struktur von CPLD wird am Beispiel des Chips der XC9500XL-Serie von Xilinx vorgestellt. CPLD kann in drei Teile unterteilt werden: Funktionsblock, FastCONNECT Ⅱ SwitchMatrix und E/A-Steuermodul. Jeder Funktionsblock besteht aus einem programmierbaren Array, einem Produktterm-Allocator und 18 Makrozellen, und die Struktur des Funktionsblocks ist in der Abbildung dargestellt. Das E/A-Steuermodul ist für die Steuerung der elektrischen Eigenschaften der Ein- und Ausgänge verantwortlich, z. B. für das Einstellen von Open-Collector-Ausgängen, Tri-State-Ausgängen usw. In Abbildung 2 sind E/A/GCK, E/A/GSR und 1/0/GTS die globalen Takt-, globalen Reset- und globalen Ausgabefreigabesignale, die über eine dedizierte Leitung mit jedem Funktionsmodul im CPLD verbunden sind.

Prinzip der CPLD-Logikimplementierung

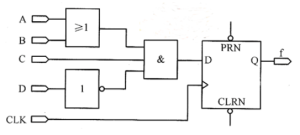

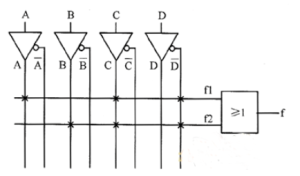

Das Folgende ist ein Beispiel für eine einfache Schaltung, die angibt, wie CPLD Logik mithilfe der obigen Struktur implementiert. Die Schaltung ist in Abbildung 4 dargestellt.

Wie funktioniert CPLD?

CPLD entwickelt außergewöhnlich dichte, schnelle und energieeffiziente programmierbare Logikgeräte unter Verwendung von CMOS EPROM, EEPROM, Flash-Speicher und SRAM-Programmiertechnologien. Sie fallen in die Kategorie der großskaligen integrierten Schaltkreise und sind relativ groß und komplex aufgebaut. Ein CPLD ist eine Art digitaler integrierter Schaltkreis, mit dem Benutzer benutzerdefinierte Logikschaltkreise nach ihren Anforderungen erstellen können. Die grundlegende Entwurfsmethode besteht darin, den Code über das Downloadkabel auf den Zielchip zu übertragen („In-System“-Programmierung), das entworfene digitale System zu realisieren und dann die entsprechende Zieldatei mithilfe der integrierten Entwicklungssoftwareplattform und der Hardwarebeschreibungssprache zu generieren.Die grundlegende Struktur von FPGA

FPGA-Architektur

Die grundlegende FPGA-Architektur verwendet Module dreier verschiedener Typen. Dazu gehören E/A-Blöcke oder Pads (CLB), Schaltmatrizen, Verbindungsleitungen und programmierbare Logikblöcke (CLB). Die grundlegende FPGA-Architektur besteht aus zweidimensionalen Arrays von Logikblöcken, die der Benutzer in beliebiger Reihenfolge verknüpfen kann. Die Funktionen eines FPGA-Architekturmoduls werden in diesem Artikel behandelt. Ein CLB (Configurable Logic Block) enthält digitale Eingänge, Ausgänge und Logik. Er führt Benutzerlogik aus. Die Logikblöcke werden durch die Verbindungsleitungen geleitet, damit sie die Benutzerlogik ausführen können. Das logikbasierte Umschalten zwischen den Verbindungsleitungen wird durch die Schaltmatrix bereitgestellt. Viele Anwendungen sind über E/A-Pads mit der Außenwelt verbunden.FPGA-Grundlagen

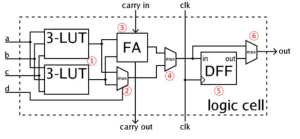

Mehrere Logikblöcke bilden einen einzelnen CLB (Abbildung 5). Die Lookup-Tabelle (LUT) eines FPGA ist eines seiner besonderen Merkmale. Eine LUT speichert eine vorgegebene Liste von Logikausgängen für jede Kombination von Eingängen; LUTs mit vier bis sechs Eingangsbits sind typisch. Flipflops, Volladdierer und Multiplexer sind einige Beispiele für gängige Logikoperationen. Die Anzahl und Konfiguration der Komponenten des CLB variieren je nach Gerät; das vereinfachte Beispiel in Abbildung 2 hat zwei LUTs mit drei Eingängen (1), einen FA (3), ein D-Typ-Flipflop (5) sowie einen normalen Multiplexer (2) und zwei Multiplexer, die in das FPGA programmiert sind.

Wie funktioniert FPGA?

Programmierbare Logik, oft als programmierbare Hardware bezeichnet, ist eine Gerätekategorie, zu der FPGAs gehören. Ein FPGA kann so konfiguriert werden, dass es praktisch jede gewünschte digitale Schaltung ist, obwohl es selbst eigentlich nichts erreicht. Das Magische an dieser Situation ist, dass sich tatsächlich nichts ändert. Das FPGA muss nur mit einer Konfiguration geladen werden, damit es wie die gewünschte Schaltung funktioniert. Kein Ärger, keine Überbrückungskabel und kein Löten. Dann kann ein FPGA so modifiziert werden, dass es sich wie noch ein weiterer Schaltkreis verhält, und noch ein weiterer, und noch ein weiterer. Da das Setup RAM-basiert ist, kann es im Grunde so oft wie nötig geändert werden. Obwohl wir die Verwendung von FPGAs zum Erstellen digitaler Schaltkreise diskutieren, konstruieren Sie Designs für sie normalerweise nicht, indem Sie Diagramme zeichnen. Sollten Sie wirklich einen Schaltplan erstellen, würde die Größe und Komplexität der Schaltkreise, die FPGAs enthalten können, ziemlich schwierig werden? Stattdessen können Sie die Tools verwenden, um einen Schaltkreis zu entwerfen, der dem Verhalten des gewünschten Schaltkreises entspricht, indem Sie das gewünschte Verhalten beschreiben.CPLD vs. FPGA-Anwendungen

CPLD-Anwendungen

- Komplexe programmierbare Logikbausteine eignen sich ideal für anspruchsvolle Steuerungsanwendungen, die eine hohe Leistung erfordern.

- Digitale Designs können CPLD für Bootloader-Aufgaben verwenden.

- Konfigurationsdaten von feldprogrammierbaren Gate-Arrays werden mithilfe der CPLD-Technologie aus einem nichtflüchtigen Speicher geladen.

- Sie werden typischerweise für einfache Designaufgaben wie die Adressdekodierung eingesetzt.

- Aufgrund ihrer geringen Größe und des niedrigen Stromverbrauchs werden CPLDs häufig in einer Vielzahl von Anwendungen eingesetzt, beispielsweise in preissensitiven, batteriebetriebenen tragbaren Geräten.

FPGA-Anwendungen

Das breite Anwendungsspektrum von FPGAs hat ihren kometenhaften Aufstieg in den letzten zehn Jahren befeuert. Zu den Anwendungen, bei denen speziell ein FPGA verwendet wird, gehören digitale Signalverarbeitung, Bioinformatik, Gerätesteuerungen, softwaredefiniertes Radio, Zufallslogik, ASIC-Prototyping, medizinische Bildgebung, Computerhardware-Emulation, Integration mehrerer SPLDs, Spracherkennung, Kryptografie, Filterung, Kommunikationscodierung und viele mehr. FPGAs werden hauptsächlich in spezialisierten vertikalen Anwendungen mit geringem Volumen verwendet. Die Top-Unternehmen investieren in die Hardwarekosten pro Einheit dieser Anwendungen mit geringem Volumen. Die verbesserte Leistungsdynamik und die Kosten haben nun die Anzahl der praktischen Anwendungen erhöht.FPGA vs. CPLD

| FPGA | CPLD |

| FPGA steht dagegen für Field Programmable Gate Arrays. | Komplexe programmierbare Logikbausteine werden als CPLDs bezeichnet. |

| RAM dient als Grundlage eines FPGA, eines digitalen Logikchips. | CPLDs hingegen basieren auf EEPROM. |

| CPLD-Verzögerungen sind viel vorhersehbarer als FPGA-Verzögerungen. | Da CPLD über nichtflüchtigen Speicher verfügt, ist es besser geschützt als FPGA. |

| FPGA fällt in die Kategorie der Feinkörnigkeit. | CPLD hingegen ist grobkörnig. |

| FPGA ähnelt einem Gate-Array. | CPLD entspricht jedoch PAL. |

| Internes Routing hat keinen Einfluss auf die Leistung von FPGA, das vertrauenswürdig ist. | Die Leistung von CPLD hingegen ist inkonsistent und vom Routing abhängig. |

| FPGA hat einen höheren Stromverbrauch. | Der Stromverbrauch von CPLD ist dagegen geringer. |

| Komplexe Apps eignen sich gut für FPGA. | Im Gegensatz dazu ist die Leistung des CPLD bei einfacheren Anwendungen besser. |

| FPGAs können bis zu 100.000 kleine Logikblöcke enthalten. | CPLDs können vergleichsweise nur einige tausend Logikblöcke speichern. |

| Ein FPGA hingegen ist ein integrierter Schaltkreis, der in erster Linie dazu bestimmt ist, nach der Produktion von einem Kunden oder Entwickler modifiziert zu werden. | Der Betrieb digitaler Systeme wird durch einen integrierten Schaltkreis, bekannt als CPLD, unterstützt. |

Das Fazit zwischen CPLD und FPGA

Einfache programmierbare Logikbausteine (SPLDs) und komplexe programmierbare Logikbausteine (CPLDs), die weniger anspruchsvolle Komponenten sind, ermöglichen die Migration von diskreten Logikbausteinen zu FPGAs der Einstiegsklasse. Die wichtigsten Merkmale von FPGAs der Einstiegsklasse sind geringer Stromverbrauch, geringe Logikdichte und minimale Komplexität pro Chip. Bausteine mit erweiterter Funktionalität fügen Funktionsblöcke mit bestimmten Funktionen hinzu: Einige Beispiele sind Hochgeschwindigkeits-Transceiver, Ethernet-MACs, PCI-Express-Controller, Phasenregelkreise (PLLs), Hochgeschwindigkeits-Serialisierer und Deserialisierer. Diese Bauelemente können entweder als eigenständige Schaltkreise (Hard-IP) entwickelt oder mithilfe von CLBs (Soft-IP) implementiert werden. Hard-IP-Blöcke steigern die Leistung auf Kosten der Rekonfigurierbarkeit. Die fortschrittlichsten System-on-Chip-Komponenten (SoC) der FPGA-Produktfamilie integrieren die FPGA-Architektur, Hard-IP und einen Mikroprozessor-CPU-Kern in einer einzigen Einheit. Ein SoC-FPGA bietet im Vergleich zu eigenständigen Geräten mehr Integration, geringeren Stromverbrauch, einen geringeren Platzbedarf auf der Platine und eine Kommunikation mit höherer Bandbreite zwischen dem Kern und zusätzlichen Blöcken.Populer Posts

ADSP-21062LCS-160

Analog Devices Inc.

SC7116VM1000

NXP Semiconductors

SAF7730HV/N231D,55

NXP Semiconductors

SAF7758HV/N205WY

NXP Semiconductors

TMS320BC53PQ57

Texas Instruments

TMS320VC5409AGWS12

Texas Instruments

TNETV2685FIDZUT9

Texas Instruments

TMS320DRE311PGE

Texas Instruments

TMS320DM6467CCUTA6

Texas Instruments

TMS320VC5409APGE12

Texas Instruments

ADSP-BF533SBBCZ400

Analog Devices Inc.

ADSP-2188MBSTZ-266

Analog Devices Inc.