Ein umfassender Leitfaden zu Xilinx FPGA: Architektur, Vorteile und wichtige Anwendungen

Globaler Lieferant elektronischer Komponenten AMPHEO PTY LTD: Umfangreiches Inventar für One-Stop-Shopping. Einfache Anfragen, schnelle, individuelle Lösungen und Angebote.

1. Einführung in Xilinx FPGA

Field Programmable Gate Arrays (FPGAs) von Xilinx sind wichtige Komponenten in verschiedenen fortschrittlichen digitalen Anwendungen. Xilinx FPGAs sind bekannt für ihre Flexibilität, Skalierbarkeit und breite Palette an IP-Core-Unterstützung und ermöglichen Ingenieuren und Designern die Entwicklung leistungsstarker, maßgeschneiderter Lösungen. Dieser Leitfaden befasst sich eingehend mit der Architektur, den Vorteilen und den wichtigsten Anwendungen von Xilinx FPGAs und bietet praktische Einblicke, die Hardware-Ingenieuren, digitalen Designern und Anfängern helfen, fundierte Entscheidungen zu treffen.

2. Die FPGA-Architektur von Xilinx verstehen

Übersicht über die FPGA-Serie

Das FPGA-Portfolio von Xilinx umfasst mehrere Serien, die jeweils für bestimmte Anwendungsfälle optimiert sind:

Produktserienvergleich

| Serie | Leistung | Energieeffizienz | Kosteneffizienz | Zielanwendungen |

|---|---|---|---|---|

| Virtex | Höchste | Mäßig | Premium | HPC, KI/ML, 5G |

| Kintex | Hoch | Gut | Mittel-Premium | Video, Medizin |

| Artix | Mäßig | Sehr gut | Wirtschaftlich | Industrie, SDR |

| Spartanisch | Einfach | Ausgezeichnet | Am wirtschaftlichsten | Verbraucher, IoT |

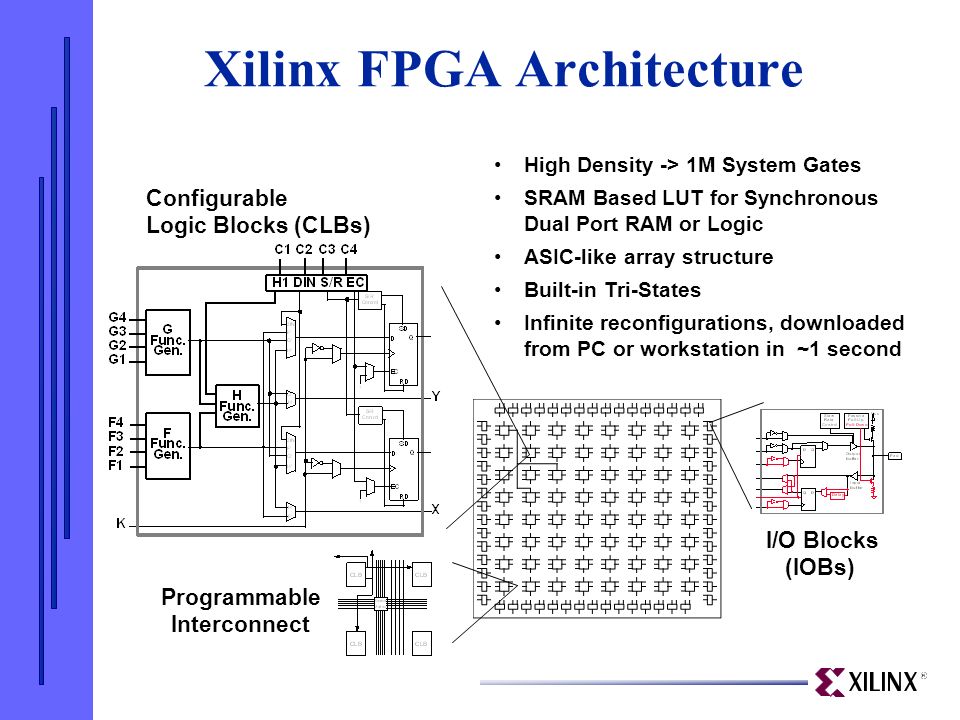

2.1 Konfigurierbare Logikblöcke (CLB)

Kernkomponenten

- Nachschlagetabellen (LUTs)

- 6-Eingangs-LUT-Architektur

- Konfigurierbar als:

- Einzelne 6-Eingangs-LUT

- Duale 5-Eingangs-LUTs

- Quad 4-Eingangs-LUTs

- Unterstützung für:

- Logikfunktionen

- ROM-Implementierung

- Verteilter RAM

- Schieberegister

- Flip-Flops

- Dual-Flip-Flop pro LUT

- Funktionen:

- Takt aktivieren

- Set/Reset-Funktionen

- Konfiguration des Anfangszustands

- Alternative D- oder Latch-Modi

- Schnelle Carry-Logik

- Dedizierte Carry-Kette

- Unterstützung für:

- Hochgeschwindigkeitsarithmetik

- Komparatoren

- Zähler

- Breite Multiplexer

CLB-Konfigurationsoptionen

- Logikmodus

LUT → FF → Ausgabe- Traditionelle kombinatorische Logik

- Elemente sequentieller Logik

- Implementierung komplexer Funktionen

- Speichermodus

LUT (als RAM) → Steuerlogik → Ausgabe- Implementierung von verteiltem Speicher

- Lokaler Hochgeschwindigkeitsspeicher

- Benutzerdefinierte Speicherkonfigurationen

2.2 Programmierbare Verbindungen

Verbindungstypen

- Schaltmatrizen

- Programmierbare Routing-Knoten

- Verbindungstypen:

- Direkte Verbindungen

- Leitungen doppelter Länge

- Lange Leitungen

- Globale Leitungen

- Routing-Ressourcen

- Lokale Verbindung

- Innerhalb von CLB-Verbindungen

- Benachbarte CLB-Verbindungen

- Pfade mit minimaler Verzögerung

- Regionale Verbindung

- Routing über mittlere Distanzen

- Clock Region Spanning

- Optimiert für gemeinsame Pfade

- Globale Verbindung

- Chipweites Routing

- Taktverteilung

- Reset-Signalverteilung

- Lokale Verbindung

Timing-Optimierung

- Verzögerungsmanagement

- Pfadverzögerungsanalyse

- Kritische Pfadoptimierung

- Implementierung von Timing-Beschränkungen

- Clock Domain Crossing

- Synchronisierungstechniken

- Verwaltung von Taktverzerrungen

- Handhabung von Metastabilität

2.3 Hochleistungs-DSP-Module

DSP48E2 Slice-Architektur

- Kernkomponenten

- 27x18-Multiplikator

- 48-Bit-Akkumulator

- Voraddierer/Subtrahierer

- Musterdetektor

- Betriebsmodi

- Multiplikation

- Multiplizieren-Akkumulieren

- Addition mit drei Eingängen

- Barrel-Shifting

- Wide-Bus Multiplexing

DSP-Anwendungen

- Signalverarbeitung

- FIR-Filter

- FFT-Berechnung

- Digitale Abwärts-/Aufwärtskonvertierung

- Korrelation/Faltung

- Arithmetische Operationen

- Festkommaarithmetik

- Gleitkommaunterstützung

- Verarbeitung komplexer Zahlen

- CORDIC-Algorithmen

Leistungsmesswerte

- Variationen der Geschwindigkeitsstufe

Geschwindigkeitsstufe Maximale Frequenz Stromverbrauch -1 300 MHz Niedrigste -2 500 MHz Mäßig -3 700 MHz Höchste - Ressourcennutzung

- Multiplizieren und akkumulieren von Operationen pro Takt

- Kennzahlen zur Energieeffizienz

- Funktionen zur gemeinsamen Nutzung von Ressourcen

Überlegungen zur Implementierung

- Designoptimierung

- Optimierung der Pipeline-Phasen

- Strategien zur gemeinsamen Nutzung von Ressourcen

- Auswahl der Taktfrequenz

- Kompromisse zwischen Leistung und Leistung

- Integrationsrichtlinien

- Schnittstellen-Timing

- Datenausrichtung

- Steuerungssignalverwaltung

- Überlegungen zum Taktbereich

Dieses architektonische Verständnis ist entscheidend für:

- Optimale Ressourcennutzung

- Leistungsmaximierung

- Stromverbrauchsmanagement

- Effiziente Designimplementierung

3. Wichtige Vorteile von Xilinx FPGA

3.1 Unübertroffene Flexibilität

Anpassbarkeit des Designs

- Neukonfiguration der Hardware

- Neukonfigurationsfunktionen zur Laufzeit

- Unterstützung für teilweise Neukonfiguration

- Mehrere Konfigurationsmodi:

- JTAG-Konfiguration

- Master/Slave Seriell

- Master/Slave Parallel

- SPI/BPI Flash

- Vorteile der Designiteration

- Vergleich der Entwicklungskosten:

Designänderungen FPGA-Kosten ASIC-Kosten Anfänglich 50.000 US-Dollar Über 500.000 US-Dollar Kleinere Überarbeitung $0 Über 100.000 US-Dollar Große Überarbeitung $0 300.000 $+

- Vergleich der Entwicklungskosten:

- Vorteile bei der Markteinführungszeit

- Fähigkeit zum schnellen Prototyping

- Schnelle Designvalidierung

- Sofortige Fehlerbehebungen

- Funktionserweiterungen ohne Hardwareänderungen

Flexibilität bei der Implementierung

- Ressourcenzuweisung

- Dynamische Ressourcenzuweisung

- Benutzerdefinierte Hardwarearchitekturen

- Optimierte Ressourcennutzung

- Skalierbare Designs

- Schnittstellenanpassung

- Unterstützung mehrerer E/A-Standards

- Konfigurierbare Spannung Ebenen

- Protokollanpassungsmöglichkeit

- Entwicklung benutzerdefinierter Schnittstellen

3.2 Umfassende IP-Core-Bibliothek

Verfügbare IP-Kategorien

- Kommunikationsprotokolle

- Ethernet (1G/10G/100G)

- PCIe Gen1-4

- JESD204B/C

- USB 2.0/3.0

- CAN/LIN/FlexRay

- Verarbeitungssysteme

- Mikroprozessorkerne

- DSP-Funktionen

- Speichercontroller

- DMA-Engines

- Spezialisierte Funktionen

Kategorie Verfügbare IPs Zeitersparnis bei der Integration KI/ML 20+ 3-6 Monate Sicht 15+ 2-4 Monate Sicherheit 10+ 4-8 Monate Audio 12+ 1-3 Monate

Vorteile der IP-Integration

- Entwicklungseffizienz

- Reduzierte Verifizierungszeit

- Bewährte Funktionalität

- Optimierte Leistung

- Professioneller Support

- Kosteneinsparungen

- Reduzierte Entwicklungsressourcen

- Geringere Verifizierungskosten

- Minimiertes Risiko

- Schnellere Markteinführung

3.3 Hohe Parallelverarbeitungsfähigkeiten

Vorteile der parallelen Architektur

- Verarbeitungsleistung

- Gleichzeitige Ausführung von Vorgängen

- Pipeline-Implementierung

- Erstellung benutzerdefinierter Datenpfade

- Deterministisches Timing

- Leistungsvergleich