Was ist Verilog?: Modul, Multiplexer und Verilog vs. Vhdl

August 02 2023

Anfrage

Globaler Lieferant elektronischer Komponenten AMPHEO PTY LTD: Umfangreiches Inventar für One-Stop-Shopping. Einfache Anfragen, schnelle, individuelle Lösungen und Angebote.

SCHNELLE ANFRAGE

ZUR RFQ-LISTE HINZUFÜGEN

Dieser Artikel bietet eine ausführliche Einführung in Verilog, einschließlich Verilog-Modul, Decoder, Multiplexer, Verilog vs. Vhdl usw.

Was ist Verilog?

Eine Hardwarebeschreibungssprache ist Verilog (HDL). Diese Sprache wird zusammen mit ihrem Rivalen VHDL am häufigsten zum Programmieren von FPGAs verwendet. Warum sollten Sie eine schwierige Programmiersprache lernen, wenn Sie ein FPGA mit einem Schaltplan programmieren können, den Sie wahrscheinlich bereits kennen und verstehen? Tatsächlich ist es bei komplexeren Designs einfacher, sie in einer Programmiersprache darzustellen, als sie zu zeichnen. Verilog verfügt über Funktionen, die denen in Programmiersprachen ähneln, wie z. B. „if“-Anweisungen, Codeblöcke und die Möglichkeit, Zahlen zu addieren und zu subtrahieren.Verilog-Tutorial

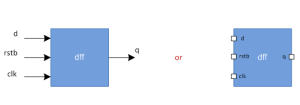

Verilog-Modul

Softwareentwickler werden feststellen, dass ein Verilog-Modul einer objektorientierten Programmierklasse ähnelt. Es definiert eine Reihe von Logik, die in Ihrem Design mehrmals instanziiert werden kann und sowohl öffentliche als auch private Eigenschaften hat. Wenn Sie Elektronik bevorzugen, betrachten Sie ein Modul als eine Unterbaugruppe des Designs mit genau definierten Verbindungen, die es ermöglichen, es mit anderen Modulen oder, wenn Sie es vorziehen, einem IC zu verbinden. Wenn die Dinge etwas komplizierter werden, kann ein einfaches Design vollständig in einem einzigen Modul enthalten sein, anstatt eine Sammlung miteinander verbundener Module zu werden. Wenn Sie es auf diese Weise tun, können Sie die Module anderer Leute in Ihren Designs verwenden.

Ein Siebensegment-Decoder

Eine Art elektronisches Anzeigegerät zur Anzeige von Dezimalzahlen ist eine Siebensegmentanzeige (SSD). Sie kann anstelle von komplizierten Anzeigen wie Punktmatrizen verwendet werden. Eine SSD enthält 7 Segmente, daher könnten wir sie theoretisch verwenden, um 27 = 128 Zeichenkombinationen anzuzeigen. Die meisten dieser Kombinationen sind jedoch für das menschliche Auge verwirrend. Auf einem 7-Segment-Panel können Dezimalzahlen angemessen dargestellt werden, wie unten gezeigt:

Entprellen von Tasten

Möglicherweise haben Sie beim Experimentieren mit dem Zählerprojekt ein Prellen des Schalters bemerkt, wodurch der Zähler einige Zahlen übersprungen hat. Indem wir ein Entprellen-Modul entwickeln, das auf jedes Projekt mit einem Schalter angewendet werden kann, können wir Maßnahmen ergreifen, um dieses Problem zu beheben. Beim Drücken von Schaltern müssen eigentlich drei Probleme gelöst werden. Das erste Problem besteht darin, dass ein Tastendruck konstruktionsbedingt nie mit der Uhr synchronisiert wird. Das zweite Problem besteht darin, wie unerwünschte Übergänge, die durch das Prellen der mechanischen Kontakte des Schalters verursacht werden, wirklich vermieden werden können.Verilog-Multiplexer

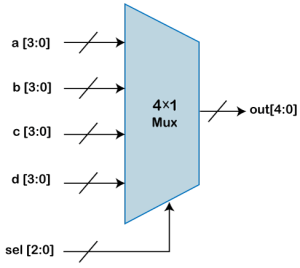

Die drei wichtigsten Methoden zum Erstellen eines Multiplexers sind die folgenden. Logikgatter bilden digitale Multiplexer, Transistoren kommen in analoge Multiplexer und rotierende Wellen in mechanische oder Drehschalter. Der MUX selbst fungiert als digital gesteuerter Mehrpositionsschalter, bei dem die Dateneingabe durch den Binärcode gesteuert wird, der auf die ausgewählten Eingänge angewendet und auf den Ausgang umgeschaltet wird. Basierend auf dem Auswahlsignal sendet er beispielsweise Daten von einem der N Eingänge an den Ausgang. Jeder der N 4-Bit-Eingänge eines 4-Bit-Multiplexers kann mittels eines Auswahlsignals an den Ausgang gesendet werden. Sel kann vier verschiedene Werte haben und ist ein 2-Bit-Eingang. Jeder Wert auf der Auswahlleitung ermöglicht es, einen der Eingänge an den Ausgang zu senden.

Verilog-Leitungen, Register und Busse

In Verilog sind die sogenannten Leitungen (die Dinge miteinander verbinden) oder Register (die Zustände speichern und eher Variablen in Programmiersprachen ähneln) das, was in einer traditionellen Programmiersprache Variablen wären. Eine einzelne Binärziffer wird als Leitung und Register bezeichnet. Ein Vektor ist eine Sammlung von Bits, die verwendet werden können, um Operationen am gesamten Vektor auszuführen, wenn an mehreren Bits gleichzeitig gearbeitet wird. Dies ist vergleichbar mit der Verwendung von Wörtern beliebiger Länge in einer herkömmlichen Programmiersprache. Die oberen und unteren Bits werden angegeben, wenn solche Vektoren definiert werden. Das folgende Beispiel zeigt einen 8-Bit-Zähler:

Integerkonstanten in Verilog

Wenn Sie in Verilog mit einem Vektor arbeiten, was Sie häufig tun werden, ist es praktisch, Werte mit Zahlen beliebiger Bitgröße und Basis (Zahlenbasis) zuzuweisen. Zu diesem Zweck verwendet Verilog eine eindeutige Zahlensyntax. Unbenutzte Bits werden auf 0 gesetzt und die Zahl wird als Dezimalzahl angenommen, wenn weder die Anzahl der Bits noch die Basis angegeben sind. Das Zahlenformat besteht aus der Anzahl der Bits, einem Apostroph, einem Basisindikator (b = binär, h = hex und d = dezimal), der Zahlenkonstante und schließlich der Zahl.Parallele Ausführung

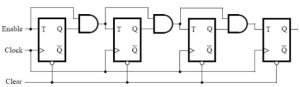

Für Designverifizierungsprojekte ist es häufig erforderlich, bestimmte Funktionsthreads parallel zu steuern. Diese Threads können verwendet werden, um die Aktivität auf einigen parallel laufenden Schnittstellen zu überwachen, gleichzeitige Stimuli zu steuern, Daten für komplexe Abdeckungsblöcke zu sammeln usw. Um das endgültige Verifizierungsziel mithilfe der Verifizierungsfunktionen zu erreichen, muss ein Benutzer einen feinen und zuverlässigen Steuerungsansatz für alle diese gleichzeitigen Funktionsthreads entwickeln.Synchronous-Logik von Verilog

Das vorherige Gegenbeispiel zeigt, wie einfach es ist, Hardware in Verilog zu definieren. Es fehlt jedoch eine entscheidende Komponente, die in praktisch jedem Verilog-Beispiel enthalten ist, das Sie sich ansehen möchten. Mit anderen Worten, es ist nicht zeitsynchronisiert. Weil es so einfach ist, funktioniert das Beispiel nur in diesem Fall. Das Problem tritt auf, sobald Projekte auch nur ein bisschen komplizierter werden, da Signale mit unterschiedlichen Geschwindigkeiten durch Logikgatter laufen, was bedeutet, dass ein Ausgang, der von Eingängen zahlreicher anderer Systemkomponenten und möglicherweise sogar vom Ausgang selbst abhängt, einige Zeit braucht, um seinen endgültigen Wert zu erreichen. Er kann fehlerhafte Impulse aufweisen, die von anderen Teilen des Systems ignoriert werden sollten. Solche Ausgänge werden als metastabil bezeichnet. Aufgrund der Tatsache, dass wir den Takteingang des Zählers als allgemeinen Eingang verwenden, der mit einem Schalter verbunden ist, und nicht als synchronisierenden Takteingang, sind Ihnen beim Erstellen des Projekts möglicherweise einige Warnmeldungen aufgefallen.Verilog-Timing-Steuerung

Um die Zeit in der Simulation voranzutreiben, sind Timing-Steuerungsanweisungen erforderlich. Timing-Steuerungen werden verwendet, um anzugeben, wann prozedurale Anweisungen ausgeführt werden. Die unten aufgeführten Zeitsteuerungen in Verilog umfassen benannte Ereignisse, flankensensitive Ereignissteuerung, Verzögerungssteuerung und pegelsensitive Ereignissteuerung. Durch Verwendung der Verzögerungssteuerung können Sie die Ausführung der Anweisung von dem Zeitpunkt an verzögern, an dem der Simulator sie erkennt, bis nach ihrer Ausführung. Das @-Zeichen in Verilog bezeichnet eine flankensensitive Ereignissteuerung, die blockiert, bis einer der Ereignisbezeichner eine Wertänderung (eine Flanke) erfährt. Anstatt dass ein Wächter blockiert, während auf das Auftreten eines Flankenereignisses gewartet wird, werden die Flankenereignisse in eine Warteschlange gestellt und dann von @(...)-Wächtern behandelt. Die Ausführung einer prozeduralen Anweisung kann verzögert werden, bis eine Bedingung erfüllt und mit dem Schlüsselwort „wait“ erfüllt wird. Und es handelt sich um eine pegelsensitive Steuerung.Ein Zähler in Verilog

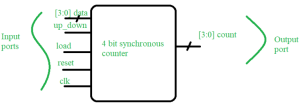

Der Zähler ist eine digitale sequentielle Schaltung, die je nach Zählrichtung (aufwärts/abwärts) von 0 bis 15 und umgekehrt zählen kann. In diesem Fall ist der Zähler ein 4-Bit-Zähler. Jede positive (steigende) Flanke des Taktzyklus führt zu einer Auswertung des Zählerwerts („count“). Wenn der Eingang „Reset“ auf logisch hoch gesetzt ist, wird der Zähler auf 0 zurückgesetzt. Wenn das Signal „Load“ logisch hoch ist, wird der Zähler mit dem Eingang „Data“ geladen. Wenn nicht, zählt er aufwärts oder abwärts. Wenn das Signal „up_down“ logisch hoch ist, zählt der Zähler aufwärts, andernfalls zählt er abwärts.

Verilog vs. SystemVerilog

Verilog ist eine Hardwarebeschreibungssprache (HDL), während System Verilog die Hardwareverifizierungssprache (HVL) und die Hardwarebeschreibungssprache (HDL) kombiniert. Während SystemVerilog zum Planen, Simulieren, Testen und Implementieren elektrischer Systeme verwendet wird, wird die Sprache Verilog zum Strukturieren und Modellieren elektronischer Systeme verwendet. Während sich die Verilog-Testumgebung auf Tests auf Modulebene konzentriert, basiert SystemVerilog auf der Testumgebung auf Klassenebene. Verilog erfordert die Verwendung von C und Fortran, aber SystemVerilog ist eine Programmiersprache, die Verilog, VHDL und C++ kombiniert. Verilog bietet nur die Datentypen Wire und Reg, im Gegensatz zu SystemVerilog, das auch die Datentypen enum, union, struct, string und class umfasst.Verilog vs. VHDL

| Verilog | VHDL |

| In VHDL wird starke Typisierung verwendet. Dadurch wird es für Anfänger schwieriger, Fehler zu machen, da der Compiler Sie daran hindert, ungültigen Code zu schreiben. | Verilog hat eine schwache Typisierung, wodurch Sie falschen, aber kürzeren Code erstellen können. |

| Verilog ähnelt einer Programmiersprache mehr als C. Dadurch ist das Lesen und Verstehen der Operationen von Verilog für jemanden, der C beherrscht, einfacher. | Obwohl VHDL ausführlicher ist und mehr Platz einnimmt, ist es tendenziell flüssiger und beim Lesen einfacher zu verstehen. |

| Verilog ist unter bestimmten Umständen nicht-deterministisch. | VHDL ist sehr deterministisch |

| Verilog verwendet normalerweise weniger Code, um dasselbe zu erreichen. Aufgabe. | VHDL erfordert viel Tipparbeit. |

| Im Gegensatz zu VHDL ist Verilog weniger für die Hardwaremodellierung auf hoher Ebene geeignet, da es nur mit einfacheren Datentypen arbeitet und keine anspruchsvollen unterstützt. | Zusätzlich zu den von der Sprache selbst bereitgestellten Standarddatentypen erlaubt VHDL, wie bereits erwähnt, auch benutzerdefinierte Datentypen, was Flexibilität und Anpassungsmöglichkeiten bietet. |

Fazit zu Verilog vs. VHDL

Das HDL, das sich vollständig im Entstehen befindet und verändert und bei dem ständig neue Funktionen eingeführt werden, heißt Verilog. Während Verilog eine schwach typisierte Sprache ist und mit allen vordefinierten Datentypen geliefert wird, ist VHDL eng typisiert und extrem ausführlich. Während Verilog die Möglichkeit der Simulationsunterstützung bietet, die die Fehlerbehebung bei designbezogenen Problemen mithilfe von Wellenformen erleichtert, die auf der Grundlage der Datenbank dargestellt und weiter untersucht werden können, bietet VHDL keine interne Simulationssteuerung als integrierte Funktion. Letztendlich ist es ratsam, dass Sie sich irgendwann in Ihrem Leben mit Verilog und VHDL beschäftigen und damit üben, da Sie in diesem Bereich mit Sicherheit auf sie stoßen werden. Am besten ist es, selbst praktisch mit ihnen zu programmieren und jede der Sprachen zu üben, um herauszufinden, welche für Sie am besten geeignet ist.Populer Posts

Abbauen Sie elektrisches Spielzeug für Mädchen, Der Verkäufer sagte, ich könnte es zur Arbeit tragen

ISPLSI1016-80LT44I

Lattice Semiconductor

LC4064V75TN100-101

Lattice Semiconductor

EPF10K100EFC484-1X

Intel

ISPGDX120A-5Q160

Lattice Semiconductor

5SGXMA4K2F40I3LCV

Intel

GAL22V10C-TLJ

Lattice Semiconductor

EP4CE40F23I8LN

Intel

LC4256C-75TN100C-10I

Lattice Semiconductor

GAL22V10B-150LP

Lattice Semiconductor

GAL16V8-125

Lattice Semiconductor

LC5256MB-4F256-75I

Lattice Semiconductor

LC4384C-75FN256I

Lattice Semiconductor