Verilog vs. VHDL: Was sind die Unterschiede zwischen ihnen

July 24 2023

Anfrage

Globaler Lieferant elektronischer Komponenten AMPHEO PTY LTD: Umfangreiches Inventar für One-Stop-Shopping. Einfache Anfragen, schnelle, individuelle Lösungen und Angebote.

SCHNELLE ANFRAGE

ZUR RFQ-LISTE HINZUFÜGEN

Dieser Artikel enthält detaillierte Informationen zu Verilog und VHDL und zeigt einige Unterschiede zwischen ihnen auf, beispielsweise hinsichtlich Syntax, Design, Ausführlichkeit usw.

Was ist Verilog?

Tatsächlich sind Hilo, eine veraltete Hardwarebeschreibungssprache, und die Programmiersprachen C die Wurzeln von Verilog. Alle vordefinierten Datentypen sind darin vorhanden, was es zu einer extrem eingeschränkten und schwach typisierten Sprache macht. Die Datentypen werden auf Bitebene angezeigt. Strings und Verilog können mit anderen Datentypen kombiniert werden. Im Vergleich zu VHDL ist die Simulationssemantik von Verilog vager. Aus diesem Grund finden Entwickler Verilog unglaublich vielseitig; Wenn jedoch Codierungsstandards nicht eingehalten werden, können aufgrund von Mehrdeutigkeiten Race-Situationen entstehen. Die Wiederverwendbarkeitsfunktion von Paketen muss bereitgestellt werden, was jedoch aufgrund des eingeschränkten Anwendungsbereichs der Sprache und der unzureichenden Paketierungsfähigkeit äußerst schwierig ist. Grundlegende Simulationssteuerungsbefehle sind in Verilog verfügbar und unterstützen die Durchführung von Systemaktivitäten. Aufgrund der voreingestellten Systemaufgaben und unkomplizierten Datentypen in Verilog werden Befehlszeilen- oder Batch-Simulationen häufig von Programmierern verwendet. Wellenformen aus der Simulation können auch zum Debuggen verwendet werden.

Was ist VHDL?

Der eigentliche Ursprung von VHDL liegt in der Programmiersprache Ada, einer sehr stark und dicht typisierten Hardwarebeschreibungssprache. VHDL ist im Vergleich zu Verilog, einem anderen HDL, aufgrund der Sprachanforderungen sehr ausführlich, was auch die Anzahl selbstdokumentierender Designs erhöht. Eine starke Typisierung in VHDL stellt sicher, dass Datentypen explizit von einem in einen anderen umgewandelt werden, beispielsweise beim Übergang von einem Bit-Vektor zu einer Ganzzahl. Die Semantik der VHDL-Sprache wurde so erstellt, dass sie äußerst klar und eindeutig ist. Die Designs von VHDL sind leicht portierbar, was auch die Funktionalität erhöht, sehr einfach von einem Tool zum anderen zu wechseln. Aus diesem Grund besteht keine Notwendigkeit, sich über Race Conditions Gedanken zu machen. Um die Nützlichkeit der Sprache zu erhöhen, stützt sich das VHDL-Design stark auf den IEEE-Standard 1164 und verwendet die Math- und Numeric-Pakete. VHDLs sind vollständig toolabhängig und bieten keine Überwachungs- oder Simulationssteuerungsfunktionen. Da VHDL-Typen benutzerdefiniert sind und keine integrierte Simulationssteuerung vorhanden ist, wird das Debuggen von Designproblemen erschwert und erfordert die Verwendung interaktiver GUIs.

Tutorial zu Verilog vs. VHDL

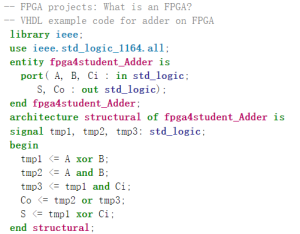

So verwenden Sie Verilog und VHDL bei der Arbeit mit FPGA

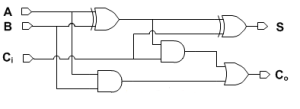

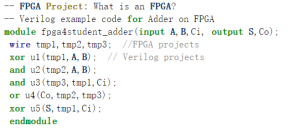

Sehen wir uns eine sehr einfache Illustration der Verwendung eines FPGA an. Nehmen wir für den Moment an, dass Sie einen 1-Bit-Volladdierer erstellen und bereits das Logikdiagramm des Addierers erhalten haben, das in der Abbildung unten dargestellt ist.

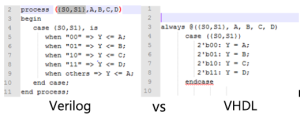

Vergleich der Syntax von Verilog und VHDL

VHSIC steht für Very High-Speed Integrated Circuit, während VHDL für VHSIC Hardware Description Language steht. VHDL steht für Very High-Speed Integrated Circuit Hardware Description Language, daher am Ende. Das ist ein ganz schöner Brocken, wenn ich je einen gehört habe. Eines der charakteristischen Merkmale von VHDL ist, dass es sich um eine eng typisierte Sprache handelt, was bedeutet, dass die Sprache selbst jeden Datentyp (Ganzzahl, Zeichen usw.) vordefiniert hat. Einer der Datentypen muss jeden in dieser Sprache angegebenen Wert oder jede Variable angemessen beschreiben. Im Vergleich zu Verilog ist VHDL ausführlicher und hat eine andere Syntax. Sie haben eine bessere Möglichkeit, mehr Codezeilen zu erstellen, wenn Sie VHDL verwenden. Außerdem kann sich die gelegentliche Verwendung von VHDL intuitiver anfühlen. VHDL kann das Programmieren natürlicher erscheinen lassen. Aber vielleicht ist das nur meine Meinung. Die Sprache ist in Verilog komprimierter, da es eher eine Sprache zum Modellieren von Hardware ist. Ähnlich wie bei der Sprache C muss eine kleine Menge Code eingegeben werden. Verilog bietet eine niedrigere Ebene von Programmierstrukturen, aber ein besseres Verständnis der Hardwaremodellierung. Verilog ist kompakter, da es weniger ausführlich ist als VHDL. Alles in allem unterscheidet sich Verilog ziemlich von VHDL. Es gibt einige Ähnlichkeiten, aber die Unterschiede überschatten diese.Verilog vs. VHDL-Design

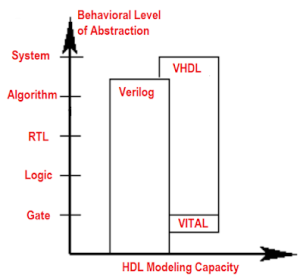

Verilog vs. VHDL: HDL-Modellierungskapazität

Sowohl Verilog als auch VHDL sind in der Lage, Hardware zu modellieren, wie die oben genannte Grafik zeigt. Verilog ist VHDL jedoch für die Hardwaremodellierung auf niedriger Ebene überlegen. Das ist sinnvoll, da Verilog von Anfang an für die Modellierung und Simulation von Logikgattern entwickelt wurde. Tatsächlich können Designer die Grundelemente in Verilog-Code instanziieren, da dieser über integrierte Grundelemente oder Logikgatter auf niedriger Ebene verfügt, während dies bei VHDL nicht der Fall ist. Zu den Gate-Primitiven in Verilog gehören and, nand, or, nor, xor, xnor, buf, not, bufif0, notif0, bufif1, pullup und pulldown. pmos, nmos, rpmos, rnmos, cmos, rcmos, tran, rtran, tranif0, rtranif0 und tranif1, rtranif1 sind Beispiele für Switch-Primitiven in Verilog. Verilog umfasst benutzerdefinierte Primitive (UDP), mit denen Designer benutzerdefinierte Zellprimitive erstellen können. Für Designer von ASICs ist diese Eigenschaft besonders wichtig und beliebt. Wie in der obigen Grafik zu sehen ist, ist VHDL Verilog jedoch in Bezug auf die Hardwaremodellierung auf hoher Ebene überlegen. Im Vergleich zu Verilog bietet VHDL zusätzliche Möglichkeiten und Konstrukte für die Hardwaremodellierung auf hoher Ebene.

Verilog im Vergleich zur Ausführlichkeit von VHDL

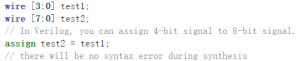

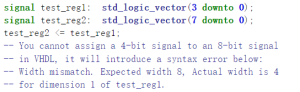

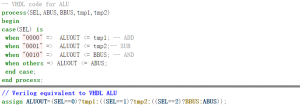

VHDL-Code muss sorgfältig mit passenden und definierten Datentypen entworfen werden, da es sich um eine sehr stark typisierte Hardwarebeschreibungssprache handelt. Wenn Sie bei der Zuweisung in VHDL Datentypen vermischen oder Signale nicht zuordnen, tritt ein Compilerfehler auf. Verilog ist jedoch eine lose typisierte Sprache. Bei der Zuweisung in Verilog können Sie Datentypen kombinieren und Signale nicht zuordnen. Ein Beispiel für VHDL-Code für nicht zuordnende Signale finden Sie unten:

Einfache Verilog-Datentypen im Vergleich zu komplexen VHDL-Datentypen

Benutzer können zusätzlich zu den zahlreichen komplexen Datentypen, die mit VHDL mitgeliefert werden, zahlreiche weitere komplizierte Datentypen definieren. Da Verilog nur zwei Hauptdatentypen hat und keine benutzerdefinierten Datentypen zulässt, ist VHDL auch ausführlicher als Verilog. Um dieselbe Schaltung darzustellen, ist VHDL-Code normalerweise ausführlicher und länger als Verilog-Code, da die starke Typisierung von VHDL Konvertierungen zwischen vielen komplexen Datentypen erfordert. Dies kann vorteilhaft oder nachteilig sein. Tatsächlich ist es wahrscheinlicher, dass der VHDL-Compiler Syntaxwarnungen hinzufügt, wenn in Ihrem VHDL-Code etwas falsch zugewiesen wurde. Im Vergleich zu Verilog ist es wahrscheinlicher, dass Ihr VHDL-Code funktioniert, wenn Sie ihn erfolgreich kompiliert haben. Im Gegensatz dazu ist Verilog schwach typisiert, kürzer und einfacher. Allerdings ist es auch nach erfolgreicher Kompilierung wahrscheinlicher, dass Ihr Verilog-Code immer noch Fehler enthält. Unten sehen Sie ein weiteres Beispielcode, der VHDL ausführlicher macht als Verilog:

Verilog vs. VHDL-Vergleich

| Verilog | VHDL |

| Durch die Verwendung der C-API-Standards wie tf, acc und vpi werden externe Schnittstellen unterstützt. | VhPI wird ebenfalls unterstützt, ist aber noch nicht standardisiert, ebenso wie die eingeschränkte Unterstützung für externe Schnittstellen, die Standards für externe Attribute verwenden. |

| Verilog bietet keine Assertion-Unterstützung. | Durch die Verwendung der C-API-Standards wie tf, acc und vpi werden externe Schnittstellen unterstützt. |

| Durch die Verwendung von Eingabe-/Ausgabedateioperationen, Fork-Join, der Generierung von Zufallszahlen und rekursiven Unterprogrammen wird die eingeschränkte Unterstützung für Verifizierungsfunktionen umgesetzt. | Zugriffstypen, verschobene Prozesse, umfassende Datei-Ein-/Ausgabeoperationen, rekursive Unterprogramme und die Erstellung von Zufallszahlen unter Verwendung eines Standardpakets werden verwendet, um die angestrebten Verifizierungsfunktionen teilweise zu erfüllen. |

| If-, if-else- und Case-Anweisungen können verwendet werden, um bedingte Anweisungen zu implementieren, und die For-Schleife kann verwendet werden, um iteratives Verhalten zu erreichen. | Die If-Anweisung und die For-Schleife können verwendet werden, um die bedingten bzw. iterativen Anweisungen zu implementieren. |

| Unterstützung für Bindung und Konfiguration in begrenztem Umfang durch Verwaltung der Instanz-zu-Modul-Bindung. | Vollständige Unterstützung für Bindung und Konfiguration dank der Möglichkeit, Komponenten zu verwalten und Instanzbindung auf neu gebildete Entitäten anzuwenden. |

| Vollständige Unterstützung für Bindung und Konfiguration dank der Möglichkeit, Komponenten zu verwalten und Instanzbindung auf neu gebildete Entitäten anzuwenden Entitäten. | Keine Möglichkeit, Elemente im laufenden Betrieb zu erstellen und zu löschen. |

| Solche Prozesse gibt es nicht. | Reaktive Bereichsprozesse können mithilfe verschobener Prozesse eingeführt werden. |

| Andere Hierarchien werden nicht unterstützt. | Durch den Einsatz verschiedener Entitäten und die Nutzung der Architektur der Schnittstelle und Implementierung können weitere Hierarchien erstellt werden. |

| Die Sprache Verilog unterstützt die Äquivalenz von Bits und Ganzzahlen. | Die teilweise Unterstützung der Äquivalenz von Bits und Vektoren Ganzzahlen kann mithilfe von Standardpaketen erfolgen. |

| Es ist nicht möglich, spärliche oder assoziative Arrays. | Durch die Verwendung von assoziativen und spärlichen Arrays können wir die verschiedenen Zugriffstypen gewissermaßen nachahmen. |

| Ereignisse mit Namen können verwendet werden. | In VHDL können wir keine benannten Ereignisse verwenden. |

| Mit Datentypen wie Bit, Bit-Vektor, Wire, Reg, unsigned, signiert, Integer, Real und gelegentlich auch Strings ist Verilog eine schwach typisierte Sprache. | Es wird eine stark typisierte Sprache verwendet. |

| Verilog unterstützt keine benutzerdefinierten Datentypen. | In VHDL werden benutzerdefinierte Datentypen unterstützt. |

Fazit zu Verilog vs. VHDL

Das HDL, das sich vollständig im Entstehen befindet und verändert und in das ständig neue Funktionen eingeführt werden, heißt Verilog. Während Verilog eine schwach typisierte Sprache ist und mit allen vordefinierten Datentypen geliefert wird, ist VHDL eng typisiert und äußerst ausführlich. Während Verilog die Möglichkeit der Simulationsunterstützung bietet, die die Fehlerbehebung bei designbezogenen Problemen mithilfe von Wellenformen erleichtert, die auf der Grundlage der Datenbank dargestellt und weiter untersucht werden können, bietet VHDL intern keine Simulationssteuerung als integrierte Funktion.Populer Posts

Abbauen Sie elektrisches Spielzeug für Mädchen, Der Verkäufer sagte, ich könnte es zur Arbeit tragen

EPM7064LC68-7

Intel

LC4128B-75TN128C

Lattice Semiconductor

EPM7160SLI84-12N

Intel

EPM7032SQC44-5

Intel

ISPGDX160VA-3B208I

Lattice Semiconductor

LC4064V-25TN44-5I

Lattice Semiconductor

ISPLSI2128E-LT176

Lattice Semiconductor

EPM7256AFC256-12T

Intel

EPM570GF256I3N

Intel

EPM7032SLC44-6F

Intel

EPM3128ATC100-5T

Intel

LCMXO1200E-3M132I

Lattice Semiconductor