Eine detaillierte Einführung in die Programmiersprache VHDL

July 24 2023

Anfrage

Globaler Lieferant elektronischer Komponenten AMPHEO PTY LTD: Umfangreiches Inventar für One-Stop-Shopping. Einfache Anfragen, schnelle, individuelle Lösungen und Angebote.

SCHNELLE ANFRAGE

ZUR RFQ-LISTE HINZUFÜGEN

Dieser Artikel bietet eine ausführliche Einführung in VHDL, einschließlich der Grundelemente von VHDL, VHDL-Codesimulation usw.

Was ist VHDL?

VHDL ist eine Sprache, die auf verschiedenen Abstraktionsebenen verwendet wird, um digitale elektrische Schaltkreise zu beschreiben. VHSIC (Very High-Speed Integrated Circuits) Hardware Description Language ist der Name des Akronyms VHDL. Dies bedeutet, dass der Designprozess durch die Verwendung von VHDL beschleunigt werden kann. VHDL ist KEINE Programmiersprache, und das kann nicht genug betont werden. Daher folgt die Fähigkeit, digitale Schaltkreise mit ihrer Syntax zu konstruieren, nicht unbedingt aus der Kenntnis ihrer Syntax. Asynchrone und synchrone Schaltkreise können mit der HDL (Hardware Description Language), genannt VHDL, beschrieben werden. Insbesondere ermöglicht VHDL die Spezifikation der Funktionalität eines Schaltkreises über Anweisungen, ähnlich wie die meisten gängigen Programmiersprachen. Dies ermöglicht nicht nur die Beschreibung der Struktur eines Schaltkreises (aus einfacheren Teilschaltkreisen). Mithilfe von Simulationstools, die den Betrieb des betreffenden Schaltkreises genau nachbilden, können in VHDL spezifizierte digitale Schaltkreise emuliert werden. Entwickler verwenden zu diesem Zweck eine Reihe von IEEE-Standardregeln, die die Syntax der Sprache und ihre Simulation beschreiben. Darüber hinaus gibt es zahlreiche Programme, die VHDL-Code in eine Datei konvertieren, die heruntergeladen und zum Programmieren eines rekonfigurierbaren Geräts verwendet werden kann. Synthese ist der Begriff für diesen Prozess. Ein bestimmtes Tool führt den Syntheseprozess auf eine präzise Weise durch, die sich deutlich von dem unterscheidet, was andere Synthesetools leisten.

Video zur VHDL-Programmierung

Grundlegende Elemente von VHDL

- Schaltkreisentität

- VHDL-Architektur

- VHDL-Objekte

- Vordefinierte VHDL-Typen

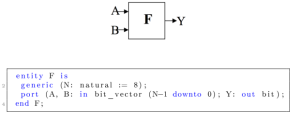

Schaltkreisentität

In der von einer Entität beschriebenen Schnittstelle kann auch eine Reihe generischer Werte enthalten sein, die zum Deklarieren der Attribute und Konstanten der Schaltkreise verwendet werden, unabhängig von der Architektur. Generika können verschiedene Zwecke erfüllen: Einerseits können sie zum Angeben von Signal- und Taktzyklusverzögerungen verwendet werden. (Diese Definitionen werden auf der Syntheseebene nicht berücksichtigt, wie später in diesem Handbuch erläutert wird.) Generische Parameter können andererseits auch als Konstanten innerhalb der Architektur verwendet werden. Diese Konstanten tragen zur besseren Lesbarkeit, Portabilität und Wartbarkeit des Codes bei. Beispielsweise kann ein generischer Parameter verwendet werden, um die Länge eines Registers (gemessen in Bits) zu bestimmen. Dies bedeutet, dass ein anderer VHDL-Code dieses Register mehrmals instanziieren kann, selbst wenn dieser Code Register mit einer anderen Anzahl von Bits instanziiert. Generische Parameter sind nicht erforderlich. Daher instanziiert eine Schaltung, die sie nicht benötigt, einfach keine generische Anweisung in der Entity-Deklaration. Die Entity einer Schaltung wird im folgenden Beispiel beschrieben. Diese Schaltung besteht aus einem einzelnen Ausgang und zwei N-Bit-Eingängen (A und B). (Y). In diesem Fall ist die generische Anweisung, die einen Parameter namens N mit einem Wert von 8 definiert, in der Entity-Beschreibung enthalten. Darüber hinaus verwendet die Deklaration der Schaltungseingänge diesen Parameter.

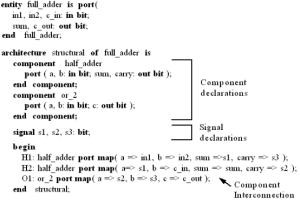

VHDL-Architektur

Der grundlegendste VHDL-Baustein ist die Entity/Architektur-Kombination. Eine Funktionalität wird durch die Kombination von Entities und Architekturen definiert. Jede Datei sollte eine einzelne Entity und Architektur haben. Große FPGA-Designs werden häufig in mehrere Entity/Architekt-Kombinationen unterteilt. Die Port-Map ist in der Entity enthalten. Die Port-Map wird verwendet, um die Eingangs- und Ausgangssignale jeder Entität anzugeben. Es gibt drei verschiedene Arten von Signalen: in, out. Die Begriffe „In“ und „Out“ sind selbsterklärend; ein „In“-Signal ist ein Eingang und ein „Out“-Signal ist ein Ausgang. Da Eingänge komplexer sind, sollten Sie sie im Allgemeinen erst verwenden, wenn Sie mit Ihren FPGA-Designs vertraut sind.VHDL-Objekte

Konstante

Objekte, denen vor der Simulation ein Anfangswert zugewiesen wird. Weder während der Schaltungssynthese noch während des Betriebs darf sich dieser Wert ändern. Sie können vor dem Start eines Prozesses oder vor dem Start einer Architektur angegeben werden. Die Deklaration einer Konstante MUSS einen Wert enthalten.

Variable

Objekte mit einem einzigen Wert, der während der Simulation oder Ausführung durch eine Zuweisungsanweisung variieren kann. In Schleifen werden Variablen häufig als Indizes oder zum Speichern von Werten verwendet, die zum Modellieren anderer Komponenten verwendet werden können. Weder physische Verbindungen noch Speicherkomponenten werden durch Variablen dargestellt. Sie können vor dem Start eines Prozesses oder vor dem Start einer Architektur angegeben werden. Einer Variablendeklaration KANN oder KÖNNTE kein Wert zugewiesen werden.![]()

Signal

Objekte, die Verbindungen zwischen Teilschaltungen oder Speicherkomponenten darstellen. Signale können im Gegensatz zu Variablen und Konstanten erstellt werden. Mit anderen Worten kann die endgültige Schaltung ein Signal physisch aus einem VHDL-Quellcode in ein Speicherelement (Flip-Flop, Register usw.) übersetzen. Vor dem Start der Architektur müssen sie deklariert werden. Da sie tatsächliche Schaltkreisverbindungen darstellen, werden die Ports einer Entität bei ihrer Erstellung automatisch als Signale deklariert.

Vordefinierte VHDL-Typen

| std_logic | Der IEEE-1164-Standard enthält eine Typdefinition. Dieser Typ stellt eine mehrwertige Logik mit neun verschiedenen möglichen Werten dar. Zu den gängigsten gehören unter anderem „0“, „1“, „Z“ (für hohe Impedanz), „X“, „U“ und „U“ (für undefiniert). |

| std_logic_vector (Bereich) | Er stellt einen Vektor von Objekten mit Mitgliedern des Typs std_logic dar. Die Regeln für Zuweisung und Definition sind identisch mit denen von std_logic. |

| bit | Es akzeptiert nur die Zahlen 0 und 1. Der Wert muss in einfache Anführungszeichen (entweder „0“ oder „1“) eingeschlossen werden, um dem Objekt zugewiesen zu werden. |

| bit_vector (Bereich) | Der bit_vector, ein Array aus 0en und 1en, hat eine feste Anzahl von Bits, die durch den Bereich angegeben wird, der immer in Klammern geschrieben wird. Ein n-Bit-bit_vector muss seinen Bereich mit der Notation N-1 bis 0 angeben. Das höchstwertige Bit (auch als MSB bekannt) befindet sich ganz links und das niedrigstwertige Bit ganz rechts. (Least Significant Bit oder LSB). Der Wert muss in Anführungszeichen gesetzt werden, um eine Zuordnung zwischen dem Element und diesem herzustellen (z. B. „0011“). |

| realer Bereich | Jede echte Zahl liegt innerhalb des Bereichs. Der Bereich ist nicht erforderlich. |

| positiver Bereich | Alles innerhalb des Bereichs, was positiv ist. Der Bereich ist nicht erforderlich. |

| natürlicher Bereich | Jede natürliche Zahl innerhalb des Bereichs. Der Bereich ist optional. |

| integerer Bereich | Jede ganzzahlige Zahl, die innerhalb des Bereichs liegt und in diesem Fall nicht in Klammern eingeschlossen ist. Beachten Sie den Bereich von 0 bis MAX. Der Bereich ist nicht erforderlich. |

| Zeichenfolge | Jede Zeichenfolge, die vollständig aus ASCII-Zeichen besteht. |

| Zeichen | Kann jeden ASCII-Wert annehmen. |

| Boolesch | Kann nur die Werte „true“ oder „false“ annehmen. |

VHDL-Code-Simulation

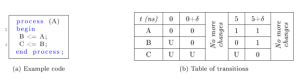

Schritte der Simulation

- Schritt 0: Der Zeitzähler wird auf 0 gesetzt und alle Signale werden initialisiert.

- Schritt 1: Alle geplanten Übergänge werden zu diesem Zeitpunkt abgeschlossen.

- Schritt 2: In der Ereignisliste werden alle Signale, die sich als Ergebnis von Übergängen ändern, die zum Zeitpunkt = t stattfinden, notiert und für den Zeitpunkt = t + geplant, wobei eine infinitesimale Zahl ist.

Simulationsanweisungen

Die in VHDL verfügbare Warteanweisung hält die Simulation des Codes an, bis eine Bedingung erfüllt ist. Wenn ein Prozess keine Sensitivitätsliste hat, muss er eine Warteanweisung enthalten. Darüber hinaus können Warteanweisungen verwendet werden, um sequentielle Hardware zu erstellen. Es gibt drei verschiedene Warteanweisungen:- Warte auf Signalliste; wenn ein Signal in der Signalliste aktualisiert wird, wird die Simulation fortgesetzt.

- Warte auf Zeit; die Simulation wird für die durch die Zeitvariable angegebene Zeit angehalten.

- Warte, bis die Bedingung erfüllt ist; bis die Bedingung erfüllt ist, wird die Simulation ausgeführt.

Simulationsvorlagen in VHDL

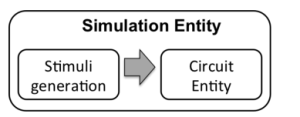

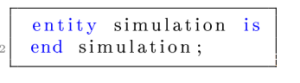

In Simulations- und Syntheseprogrammen ist häufig eine grafische Benutzeroberfläche (GUI) enthalten, um die Zuweisung des Stimulus zu den Schaltungseingängen und das Testen der Funktionalität des Designs zu vereinfachen. Für komplexe Schaltungen und große Prüfstände ist es jedoch viel praktischer, einen Prüfstand direkt mit VHDL zu erstellen. Die Testbench wird letztendlich eine VHDL-Datei sein, die eine Entität ohne Eingaben oder Ausgaben enthält, die zwei Prozesse und eine Komponente instanziiert, wie in Abbildung 11 gezeigt, unabhängig davon, ob die Testbench mithilfe der GUI oder durch direkte Eingabe generiert wurde. Letzteres erstellt tatsächlich die Testschaltung.

Es muss eine Entität ohne Ein- und Ausgänge erstellt werden.

Vorlage für VHDL-Architektur

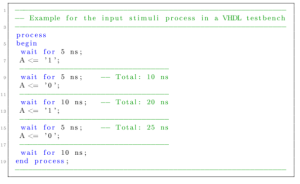

Die Methoden und Komponenten der getesteten Schaltung (sofern vorhanden) sowie die Architektur werden besprochen. Das Folgende ist eine mögliche Vorlage für die Methode zum Setzen von Stimuli auf die Eingangssignale der getesteten Schaltung:

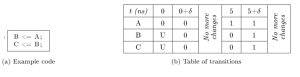

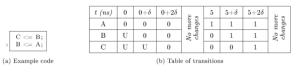

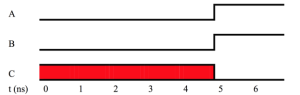

Signalsimulation

Dank der ersten Wartezeit im Code (200 ns warten;) wird das Eingangssignal für die ersten 200 ns auf seinem Startwert ('0') gehalten. Anschließend werden die nachfolgenden Anweisungen, einschließlich der Zuweisung input = „1“, ausgeführt. Dieser aktualisierte Wert bleibt durch die zweite Wartezeit (wait for 100 ns) für weitere 100 ns erhalten. Eine weitere Veranschaulichung bietet der folgende Code:

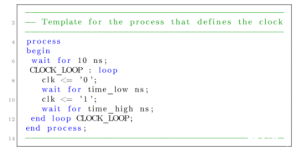

Vorlage für den Prozess, der die Uhr definiert

Diese Methode generiert ein Signal (clk), dessen Wert durch die Verwendung der Schleifenanweisung je nach den in den Konstanten time_low und time_high angegebenen Zeiten abwechselnd auf „0“ und „1“ gesetzt wird. Während der ersten 10 ns behält die erste Warteanweisung den Anfangswert von CLK bei. Die zweite Verzögerung zeigt, wann clk auf seinen niedrigen Wert („0“) gesetzt wird, danach. Die letzte Wartezeit zeigt, wann clk zuletzt auf seinen hohen Wert („1“) gesetzt wurde. Dieses Muster wiederholt sich immer wieder. Beachten Sie, dass die Schleifenanweisung dies ermöglicht. Tatsächlich besteht zwischen dieser und den Anweisungen in der For-Schleife und der While-Schleife ein kleiner Unterschied.

Populer Posts

Abbauen Sie elektrisches Spielzeug für Mädchen, Der Verkäufer sagte, ich könnte es zur Arbeit tragen

EPM7128EQC100-12

Intel

LCMXO24000HC6BG256IES

Lattice Semiconductor

LC4256V75FN256C-5N-1

Lattice Semiconductor

ISPLSI2032VE-200LT48

Lattice Semiconductor

5SGXEA7N1F40C2L

Intel

LC4064ZC-75MN2

Lattice Semiconductor

LC4128B-75T100-101

Lattice Semiconductor

5SGXMA5K2F40I3WN

Intel

10AX027H1F34I1SG

Intel

ISPGDX160V-7B272

Lattice Semiconductor

5SGXEH40I2LAA

Intel

PLMQ7192/256-160NC

Intel