Faseroptisches chaotisches Verschlüsselungssystem basierend auf FPGA

Globaler Lieferant elektronischer Komponenten AMPHEO PTY LTD: Umfangreiches Inventar für One-Stop-Shopping. Einfache Anfragen, schnelle, individuelle Lösungen und Angebote.

Hier ist ein praktischer, ingenieurfreundlicher Entwurf für ein faseroptisches chaotisches Verschlüsselungssystem auf Basis von FPGA, plus das, was aus der jüngsten Literatur bekannt ist, Kompromisse und ein minimaler HDL-Kern, um Sie zu beginnen.

Was „Chaos-Verschlüsselung über Glasfaser“ bedeuten kann (2 praktikable Architekturen)

-

Rein digitale Chaoserzeugung im FPGA + Standard-Optiklink (für Produkte empfohlen)

-

Das FPGA generiert einen chaotischen Schlüsselstrom (z. B. aus Logistik-/Tent-/Lorenz-Abbildungen), führt eine Stream-Chiffre/XOR-Verschlüsselung durch und moduliert die verschlüsselten Bits auf eine herkömmliche optische Übertragung (PAM-4, QPSK/16QAM).

-

Vorteile: Funktioniert mit handelsüblichen optischen Modulen (SFP28/CFP/Analog-Frontends), gut validierbar, skalierbar bis 10–400 Gb/s. Viele veröffentlichte Chaos-Chiffren auf FPGA.

-

-

Physikalische Chaosoptik mit Lasersynchronisation (Forschung/fortgeschritten)

-

Ein Halbleiterlaser (z. B. DFB) wird über Rückkopplung/Injektion in einen chaotischen Zustand gebracht, die Nachricht darin eingebettet (Maskierung, Chaos-Shift-Keying) und am Empfänger über Synchronisation wiedergewonnen.

-

Das FPGA übernimmt Hochgeschwindigkeits-DAC/ADC, Entzerrung, Takt-/Trägerwiedergewinnung, schlüsselabhängige Parameter und FEC. Forschungsergebnisse zeigen bereits Übertragungen mit 100 Gb/s und 800–8190 km Reichweite – jedoch noch nicht für Serienprodukte geeignet.

-

Systemblockdiagramm (Text)

Tx (FPGA)

-

Schlüssel & Sitzungsverwaltung → Chaos-PRNG-Kerne (mehrere Abbildungen gemischt) → Stream-Chiffre (XOR/Add über GF(2^n)) → Framer/FEC (z. B. KP4/RS) → Mapper (PAM-4 / QPSK/16QAM) → DACs

-

Optik: Treiber → IQ-Modulator oder MZM → EDFA/VOA/OSNR-Management → Glasfaser

Rx (FPGA)

-

Koherenter/IMDD-Empfänger → ADCs → Taktrückgewinnung → CD/PMD-Entzerrung + Equalizer → Träger-/Phasenwiedergewinnung → De-Framing/FEC → Entschlüsselung (gleicher Chaos-PRNG) → Klartext

(Bei physikalischem Chaos zusätzlich: chaotischer Laser mit Rückkopplung am Tx, synchronisierter Laser am Rx.)

Zentrale FPGA-Bausteine

-

Chaotische PRNG-Kerne: Parallelisierte diskrete Abbildungen (Logistik, Tent, Chebyshev, Lorenz), mit Whitening (z. B. Xorshift/LFSR).

-

Chaos-basierte Stream-Chiffre: Schlüsselstrom K →

C = P ⊕ Koder Modulo-Addition. Lässt sich auch mit AES/ZUC kombinieren. -

High-Speed-I/O und DSP: SerDes bis 112 Gb/s, PAM-4 oder kohärente DSP-Blöcke (CD/PMD-Kompensation, Carrier Recovery).

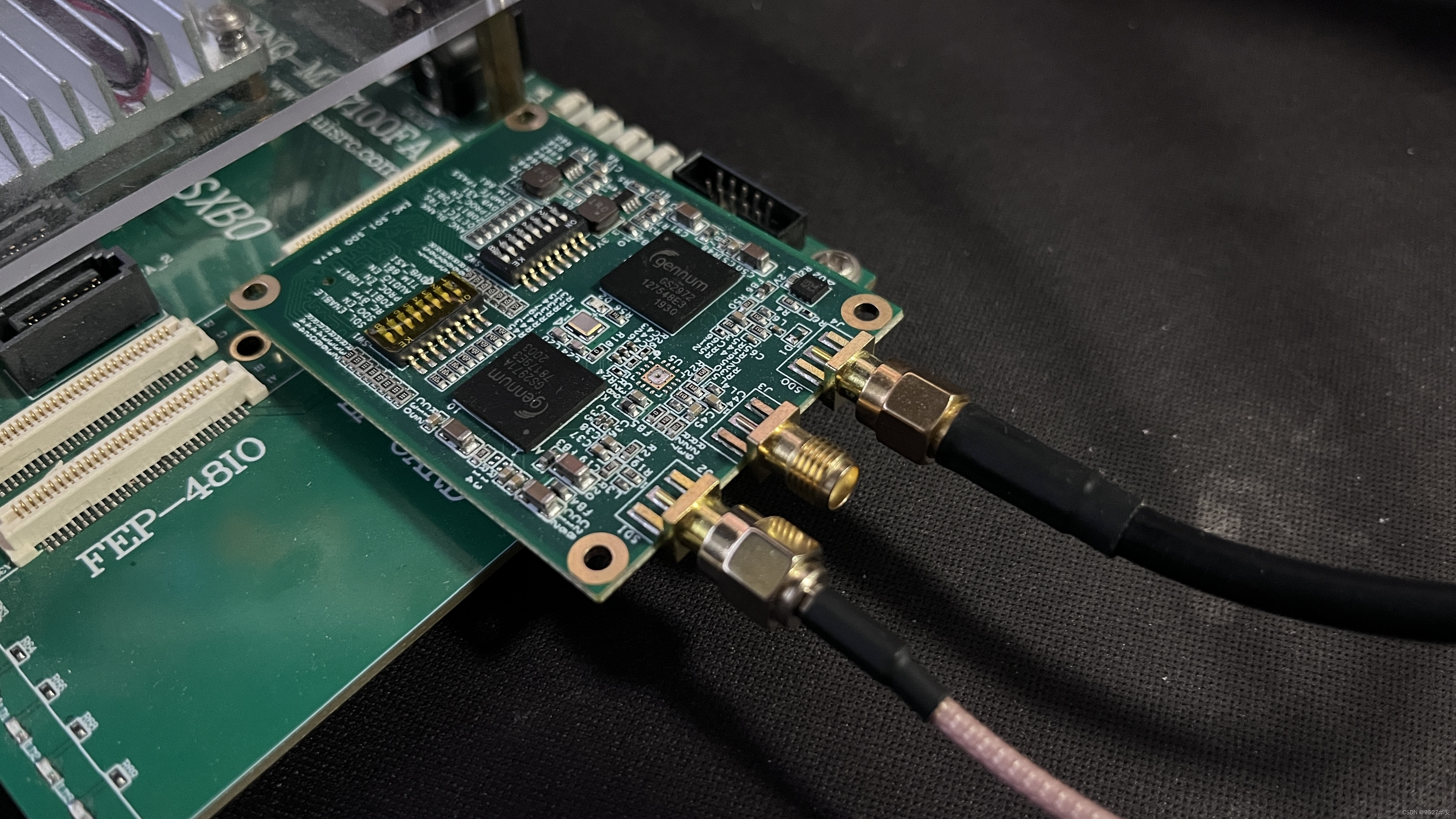

Optische Hardware (typische Komponenten)

-

Tx: DFB/ECL-Laser → IQ-Modulator oder MZM, RF-Treiber, VOA, EDFA, Isolator.

-

Rx: Koherenter Empfänger (90°-Hybrid + Balanced-PDs) oder APD/PD mit TIA → Hochgeschwindigkeits-ADCs.

-

Chaosoptik (Forschung): Laser mit optischer Rückkopplung oder gegenseitiger Injektion; Delay-Linie, OC/ISO.

Minimaler HDL-Sketch (Logistische Abbildung, Q1.31)

Sicherheitshinweise

-

Endliche Präzision reduziert Chaos → Risiko schwacher Schlüsselströme; deshalb mit bewährten Verfahren (AES-GCM, ZUC) kombinieren.

-

Chaos auf physikalischer Ebene ist interessant, ersetzt aber keine Kryptographie; eher als zusätzliche Schutzschicht nutzen.

Leistungsziele

-

Durchsatz: Keystream ≥ Datenrate (z. B. ≥100 Gb/s → ≥4 parallele PRNG-Lanes).

-

Ressourcen: Chaos-PRNG < 10 k LUTs je Lane; für kohärente DSP benötigt man High-End-FPGAs (UltraScale/Stratix-10/Agilex).

-

Latenz: < 1 µs im Cipher-Pfad, einige 10 µs im kohärenten DSP.

-

Reichweite: Forschung zeigt >800 km, teils bis 8190 km.

Test/Validierung

-

Zufälligkeit: NIST SP 800-22, Dieharder.

-

Sicherheitsvergleich: Gegen AES-GCM/ZUC messen.

-

Link-Performance: BER/FER vs. OSNR, Dispersion/PMD.

-

Chaos-Laser: Synchronisationsbereich, Zeitverzögerungssignatur (TDS) testen.

Kurzfassung

Ein faseroptisches Chaos-Verschlüsselungssystem auf FPGA-Basis kann digital (Chaos-PRNG + normale Optik) oder physikalisch (chaotische Laser mit Synchronisation) realisiert werden.

Digital ist praktikabel für Produkte (10–400 Gb/s), physikalisch aktuell eher Forschung. FPGA-Bausteine: Chaotische PRNGs, Stream-Chiffre, FEC, SerDes, DSP. Für Sicherheit empfiehlt sich die Kombination mit klassischen Verfahren (AES/ZUC). Moderne Forschung zeigt bereits 100 Gb/s Links und mehrere tausend Kilometer Reichweite.

Verwandte Artikel

- ·Beispiele für Embedded-Entwicklungsanwendungen in Automotive-ECUs

- ·Wie implementiert man Ethernet-Kommunikation in einem FPGA?

- ·Wie verbindet man einen externen Speicher mit einem FPGA?

- ·Anwendung von STM32 in digitalen Stromversorgungen

- ·Entwurf eines Ampelsteuerungssystems auf FPGA-Basis

- ·Wie implementiert man UART, SPI oder I2C in einem FPGA?

- ·Was sind die Hauptanwendungen von DSP in realen Szenarien?

- ·Entwurf eines multifunktionalen Roboterarmsystems mit Gestenerkennungssteuerung auf Basis der FPGA-Technologie

- ·Entwurfstechniken zur Reduzierung des FPGA-Stromverbrauchs