D vs. T vs. JK vs. SR Flip-Flop: Die wichtigsten Unterschiede

Globaler Lieferant elektronischer Komponenten AMPHEO PTY LTD: Umfangreiches Inventar für One-Stop-Shopping. Einfache Anfragen, schnelle, individuelle Lösungen und Angebote.

Was ist ein Flipflop?

Ein Flipflop ist ein Schaltkreis mit zwei stabilen Zuständen. Binäre Daten, die durch die Verwendung unterschiedlicher Eingänge verändert werden können, werden in diesen stabilen Zuständen gespeichert. Die wesentlichen Komponenten des digitalen Systems sind Flipflops. Beispiele für Datenspeicherkomponenten sind Flipflops und Latches. Das Flipflop dient als primäre Speicherkomponente in einem sequentiellen logischen Schaltkreis. Die grundlegenden Komponenten des Speichers sind Latches und Flipflops, sie funktionieren jedoch unterschiedlich. Flipflops können als D-Flipflops, T-Flipflops, JK-Flipflops und SR-Flipflops klassifiziert werden.

Was sind Latches?

Ein Latch ist eine Art Logikschaltung, die in der digitalen Elektronik verwendet wird; er wird manchmal als bistabiler Multivibrator bezeichnet. Da er sowohl in aktiven hohen als auch in aktiven niedrigen Pegeln existieren kann, die beide stabile Zustände sind. Indem er die Daten über einen Rückkopplungsweg speichert, funktioniert er wie ein Speichergerät. Solange das Gerät eingeschaltet ist, behält es 1 Bit an Informationen. Sobald die Aktivierung erklärt ist, kann der Latch die gespeicherten Daten sofort ändern. Sobald das Aktivierungssignal eingeschaltet ist, testet er kontinuierlich die Eingänge. Je nachdem, ob das Aktivierungssignal hoch oder niedrig ist, können diese Schaltungen in zwei Zuständen arbeiten. Beide Ein-/Ausgabesignale sind niedrig, wenn sich der Latch-Schaltkreis in einem aktiven hohen Zustand befindet. Ähnlich verhält es sich, wenn sich der Latch-Schaltkreis dann in einem aktiven niedrigen Zustand befindet, dann sind beide Ein-/Ausgabesignale hoch.

Video zu Flip-Flop

Flip-Flop vs. Latches

| Latches | Flip-Flop |

| Ein asynchroner Block ist ein Latch. Die kombinatorischen Funktionen, die die Eingangssignale für das Latch bereitstellen, müssen daher wettlauffrei sein. Andernfalls könnten sie Fehler erzeugen, die zu Latches führen und so Ihr System gefährden könnten. | Der Zustand eines Flip-Flops ändert sich dagegen nur, wenn ein Steuersignal von hoch auf niedrig oder von niedrig auf hoch wechselt. |

| Die Ausgabe des aktuellen Zustands und die Eingabe des nächsten Zustands werden beide durch den Pegel des Latch beeinflusst, der eine binäre Eingabe von entweder 1 oder 0 ist. | Die Eingabe und Ausgabe des nächsten Zustands eines Flipflops ändern sich, wenn sich der Taktimpuls ändert, der entweder ein positiver (+ve) oder ein negativer (-ve) Taktimpuls sein kann. |

| Latches arbeiten mit einem Aktivierungssignal und sind extrem empfindlich. | Flipflops sind flankenempfindlich. |

| Latching verkürzt die Taktperiode für ASICs mit hohem Taktversatz erheblich. | Die Auswirkung des Taktversatzes wird selbst bei schnell gepulsten Flipflops mit null Rüstzeit nicht verringert, da sie nicht transparent sind. |

| Logikgatter können verwendet werden, um sequentielle Schaltungsbausteine, sogenannte Latches, zu erstellen. | Sequentielle Schaltungen verwenden ebenfalls Flipflops als Bausteine, Latches können jedoch auch zum Erstellen von Flipflops verwendet werden. |

| Um unvorhersehbares Verhalten zu verhindern, erfordert DFT Latches als Sperrzustand an den Taktdomänenübergängen in der Scan-Kette. | Verwenden Sie scannbare (steuerbare und beobachtbare) Flops in DFT. |

| Erfordert mehr manuelle Berechnungen und Toolmanipulation, um sicherzustellen, dass das Timing eingehalten wird. | Durch die Verwendung von Techniken zur statischen Timing-Analyse (STA) lässt sich das Design-Timing ganz einfach überprüfen. |

| Zyklus-Ausleihe, um die Einrichtungszeit für den folgenden Registerschritt zu verlängern, vorausgesetzt, dass jede Schleife einen vollständigen Zyklus lang ausgeführt wird. Designer berücksichtigen zeitliche Fehlanpassungen und untersuchen Latches, um diese zu korrigieren. | Daten müssen vor der folgenden steigenden Flanke eingerichtet werden, da sie bei einer steigenden Flanke gestartet werden. Das System versagt, wenn es zu spät ist. Aufgrund der rauen Kanten in Flops geht Zeit verloren, selbst wenn sie früh eintreffen. |

Fazit zu Flip-Flop vs. Latches

Latches sind asynchron, während Flip-Flop synchron ist. Latches sind unglaublich empfindlich und arbeiten mit einem Aktivierungssignal, während Flip-Flops flankenempfindlich sind. Darüber hinaus unterscheiden sich ein Latch und ein Flipflop darin, dass ein Latch pegelgesteuert ist (was bedeutet, dass sich die Ausgänge ändern können, sobald sich die Eingänge ändern), während ein Flipflop flankengesteuert ist (was bedeutet, dass es seinen Zustand nur ändert, wenn ein Steuersignal von hoch auf niedrig oder von niedrig auf hoch wechselt). Bei Ihrem Design müssen Latches immer besondere Aufmerksamkeit gewidmet werden.

Flipflop-Typen

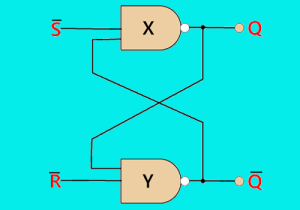

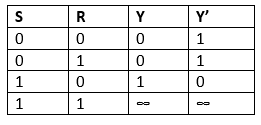

SR-Flipflop

Das SR-Flipflop ist der Flipflop-Typ, der in digitalen Systemen am häufigsten verwendet wird. Wenn der Set-Eingang „S“ in einem SR-Flipflop wahr ist, ist der Ausgang Y hoch und Y' niedrig. Wenn die Ausgänge hergestellt sind, muss die Verdrahtung der Schaltung beibehalten werden. Bis der Set- oder Reset-Eingang hoch ist oder die Stromversorgung abgeschaltet wird, bewahren wir die Verdrahtung.

Die Wahrheitstabelle von SR Flip Flop

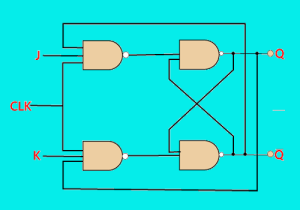

JK-Flipflop

Das JK-Flipflop wird verwendet, um den Nachteil des SR-Flipflops, undefinierte Zustände zu haben, zu überwinden. Das SR-Flipflop wird modifiziert, um das JK-Flipflop zu erstellen. Das JK-Flipflop wird durch die Erweiterung des SR-Flipflops erstellt. Das SR-Flipflop erzeugt einen Fehler, wenn die S- und R-Eingänge beide auf „true“ gesetzt sind. Das JK-Flipflop erzeugt jedoch die gewünschten Ergebnisse. Wenn beide Eingänge eines JK-Flipflops unterschiedlich sind, nimmt der Ausgang Y an der nächsten Taktflanke den Wert von J an. Der Ausgang wechselt von einem Zustand in den anderen, wenn beide Eingänge an der Taktflanke hoch sind, andernfalls passiert nichts. Im digitalen System fungiert das JK-Flipflop als Set- oder Reset-Flipflop.

Die Wahrheitstabelle des JK-Flipflops

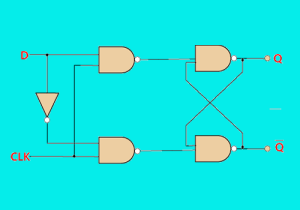

D-Flipflop

Das D-Typ-Flipflop behebt eines der Hauptprobleme der grundlegenden SR-NAND-Gatterschaltung, nämlich dass es die Eingangsbedingungen SET = „0“ und RESET = „0“ verbietet. Der Rückkopplungs-Latch-Vorgang wird durch diesen Zustand überschrieben, wodurch beide Ausgänge auf logisch „1“ gezwungen werden und der Eingang, der zuerst den Logikpegel „1“ erreicht, die Kontrolle verliert, während der Eingang, der sich noch auf logisch „0“ befindet, den Endzustand des Latchs steuert. Um dies zu vermeiden, kann zwischen den Eingängen „SET“ und „RESET“ ein Inverter eingefügt werden, um eine andere Art von Flipflop-Schaltung zu erzeugen, die als Datenlatch, Verzögerungs-Flipflop, bistabiles D-Typ-Flipflop, D-Typ-Flipflop oder einfach als D-Flipflop bezeichnet wird, wie es allgemein bekannt ist.

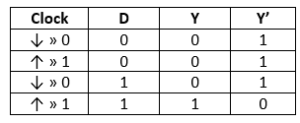

Die Wahrheitstabelle des D-Flipflops

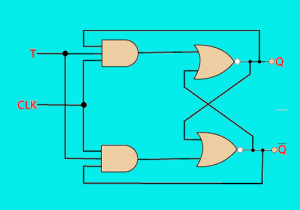

T-Flipflop

T-Flipflop wird verwendet, genau wie das JK-Flipflop. T-Flipflops haben nur einen einzigen Eingang

mit dem Takteingang verbunden, im Gegensatz zu JK-Flipflops. Durch die Verbindung beider Eingänge des JK-Flipflops zu einem einzigen Eingang entsteht das T-Flipflop. Toggle-Flipflop ist ein anderer Name für das T-Flipflop. Das Komplement seines Zustands kann in diesen T-Flipflops gefunden werden.

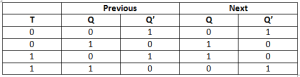

Die Wahrheitstabelle des T-Flipflops

D vs. T vs. JK vs. SR-Flipflop

| D Flip-Flop | T Flip-Flop | JK Flip-Flop | SR-Flipflop |

| Ein einzelner Dateneingang (D) plus ein Takteingang (CLK) bilden das D-Flipflop. | Die Umschalt- (T) und Takteingänge (CLK) am T-Flipflop sind beide vorhanden. | Das JK-Flipflop verfügt über einen Takteingang (CLK), zwei Eingänge (J für Set) und K für Reset. | Das SR-Flipflop verfügt über einen Takteingang (CLK), zwei Eingänge (S für Set) und R für Reset. |

| Nur wenn das Taktsignal von niedrig auf hoch wechselt (steigende Flanke), ändert sich der Ausgang (Q) des D-Flipflops entsprechend den Eingangsdaten (D). | Wenn das Taktsignal von niedrig auf hoch wechselt (steigende Flanke), schaltet der Ausgang (Q) des T-Flipflops seinen Zustand (0 auf 1 oder 1 auf 0) basierend auf dem Eingangs-Umschaltsignal (T) um. | Der Ausgang (Q) des JK-Flipflops variiert je nach den Eingangssignalen (J und K) und dem Taktsignal (CLK). | Die Eingangssignale (S und R) und das Taktsignal (CLK) des SR-Flipflops beeinflussen den Ausgang (Q), der dann variiert. |

| Bei jedem Taktzyklus zeichnet es die Eingangsdaten auf und sendet sie an den Ausgang. | Die Ausgabe ändert sich nicht, wenn T 0 ist; wenn T jedoch 1 ist, wechselt die Ausgabe in ihren komplementären Zustand. | Die Ausgabe (Q) variiert je nach den Eingangssignalen (J und K), wenn CLK von niedrig nach hoch wechselt (ansteigende Flanke), wie folgt: Wenn J=0 und K=0, bleibt das Ergebnis unverändert. J=0 und K=1 führen zu einer 0 als Ausgabe. J=1 und K=0 führen zu einer 1 als Ausgabe. Der Ausgang wechselt (kippt) seinen Zustand, wenn J=1 und K=1. | Der Ausgang (Q) variiert in Übereinstimmung mit den Eingangssignalen (S und R), wenn CLK von niedrig nach hoch wechselt (steigende Flanke), wie folgt: Wenn sowohl S als auch R Null sind, bleibt das Ergebnis unverändert. Der Ausgang wird auf 0 zurückgesetzt, wenn S=0 und R=1. S=1 und R=0 führen zu einer 1 als Ausgang. Das Ergebnis ist unerwartet (ein unerwünschter Zustand), wenn S=1 und R=1. |

| Das beliebteste Flipflop und ein fester Bestandteil sequentieller Schaltungen ist das D-Flipflop. | Bei der Frequenzteilung und beim Aufbau anderer Flipflops wird häufig das T-Flipflop verwendet. | Im Vergleich zum D- oder T-Flipflop ist das JK-Flipflop anpassungsfähiger und hat ein breiteres Anwendungsspektrum. | Aufgrund des schlechten Verhaltens des SR-Flipflops, wenn beide Eingänge auf 1 gesetzt sind, wird es seltener verwendet. |

Fazit zu D vs. T vs. JK vs. SR-Flipflop

Die JK- und SR-Flipflops haben jeweils einen Anschluss, und die T- und D-Flipflops haben jeweils einen Anschluss. Ein Daten-Flipflop oder D-Flipflop speichert je nach Eingang (0 oder 1) entweder 0 oder 1, was bedeutet, dass der Ausgang unabhängig vom Eingang mit dem Eingang übereinstimmt (speichert). T-Flipflop, das 0 für Eingang 1 speichert und den Ausgang für Eingang 1 umschaltet. Eine Variante oder Erweiterung des SR-Flipflops ist das JK-Flipflop. Das SR-Flipflop hat den Nachteil, dass keiner der Eingänge HIGH sein sollte, wenn die Uhr ausgelöst wird. Dies wird als falscher Eingangszustand angesehen, und wenn dieser Umstand eintritt, ist der Ausgang unvorhersehbar. Ein JK-Flipflop und ein SR-Flipflop unterscheiden sich hauptsächlich darin, dass ein JK-Flipflop zulässt, dass beide Eingänge HIGH sind. Der Q-Ausgang schaltet um, was bedeutet, dass er zwischen HIGH und LOW wechselt, wenn sowohl der J- als auch der K-Eingang HIGH sind. Dadurch wird die ungültige Situation, die beim SR-Flipflop auftritt, beseitigt.