Wie erzeugt man niedrige Taktfrequenzen in FPGA?

Globaler Lieferant elektronischer Komponenten AMPHEO PTY LTD: Umfangreiches Inventar für One-Stop-Shopping. Einfache Anfragen, schnelle, individuelle Lösungen und Angebote.

Für die Erzeugung niedriger Taktfrequenzen in FPGAs gibt es mehrere bewährte Methoden, die unterschiedliche Vor- und Nachteile bieten:

1. Taktteilung mit Zählern (einfachste Methode)

module Taktteiler ( input clk, // Eingangstakt (z.B. 50MHz) input reset, output reg slow_clk // Geteilter Takt ); parameter TEILER = 50_000_000 / 2; // 2Hz aus 50MHz reg [31:0] zaehler; always @(posedge clk or posedge reset) begin if (reset) begin zaehler <= 0; slow_clk <= 0; end else if (zaehler == (TEILER/2)-1) begin zaehler <= 0; slow_clk <= ~slow_clk; end else begin zaehler <= zaehler + 1; end end endmodule

Vorteile:

-

Einfache Implementierung

-

Geringer Ressourcenverbrauch

Nachteile:

-

Nur ganzzahlige Teilung möglich

-

Potenzielle Glitches

2. Pulsgenerierung (Taktfreigabe)

module Pulsgenerator ( input clk, input reset, output puls ); parameter PERIODE = 50_000_000; // 1 Sekunde bei 50MHz reg [31:0] zaehler; assign puls = (zaehler == PERIODE-1); always @(posedge clk or posedge reset) begin if (reset) begin zaehler <= 0; end else if (puls) begin zaehler <= 0; end else begin zaehler <= zaehler + 1; end end endmodule

Vorteile:

-

Keine neuen Taktdomänen

-

Bessere Timing-Eigenschaften

3. PLL-Nutzung (präziseste Methode)

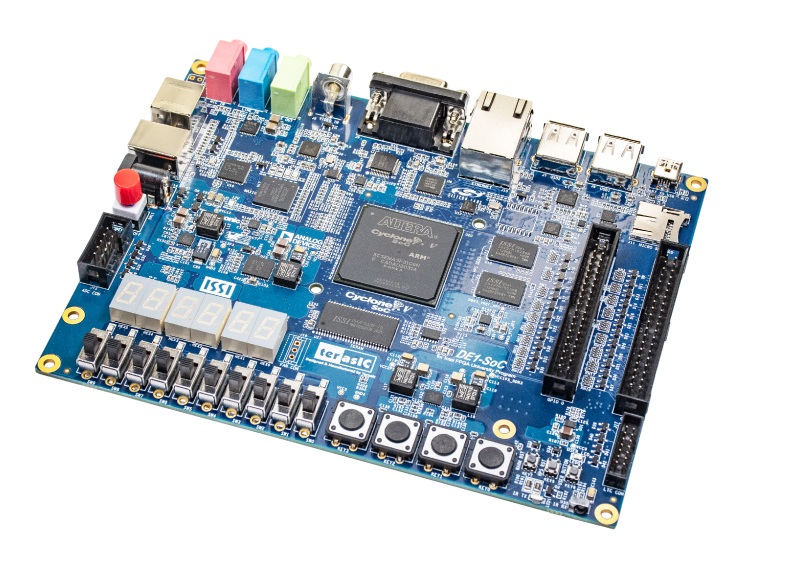

Für die DE1-SoC (Cyclone V):

-

PLL-IP-Kern in Quartus Platform Designer einbinden

-

Konfiguration:

-

Eingangsfrequenz (z.B. 50MHz)

-

Gewünschte Ausgangsfrequenz einstellen

-

Ggfs. Phasenverschiebung anpassen

-

// PLL-Instanziierung sys_pll pll_inst ( .refclk(CLOCK_50), // 50MHz Eingang .rst(reset), .outclk_0(clk_1hz), // 1Hz Ausgang .locked(pll_locked) );

4. Kombinierter Ansatz (PLL + Zähler)

-

PLL erzeugt mittlere Frequenz (z.B. 1MHz)

-

Zähler teilt weiter auf Ziel-Frequenz herunter

Wichtige Hinweise für die DE1-SoC:

-

Taktsignal-Integrität:

-

Immer dedizierte Taktpuffer (BUFG) verwenden

-

Taktgatterung vermeiden

-

-

Timing Constraints:

create_clock -name clk_50mhz -period 20 [get_ports CLOCK_50] create_generated_clock -name clk_1hz -source [get_pins pll_inst|outclk_0] \ -divide_by 50_000_000 [get_nets clk_1hz]

-

Besonderheiten des Cyclone V:

-

4 PLLs pro FPGA verfügbar

-

Minimale Ausgangsfrequenz ~1-5MHz

-

Für sehr niedrige Frequenzen (<1Hz) Zähler verwenden

-

Empfehlungen:

-

Für einfache Anwendungen: Zähler-basierte Lösung

-

Für präzise Takte: PLL nutzen

-

Für synchrones Design: Taktfreigabe (Clock Enable) bevorzugen

-

Immer richtige Constraints definieren

Verwandte Artikel

- ·Wie verbindet man einen externen Speicher mit einem FPGA?

- ·Entwurf eines Ampelsteuerungssystems auf FPGA-Basis

- ·Faseroptisches chaotisches Verschlüsselungssystem basierend auf FPGA

- ·Wie implementiert man UART, SPI oder I2C in einem FPGA?

- ·Entwurf eines multifunktionalen Roboterarmsystems mit Gestenerkennungssteuerung auf Basis der FPGA-Technologie

- ·Entwurfstechniken zur Reduzierung des FPGA-Stromverbrauchs

- ·Kosten-Effektivität im Vergleich: Altera vs Xilinx vs Lattice

- ·Wie bootet man Linux auf einem Xilinx FPGA?

- ·Ist ein FPGA-Chip für die Algorithmusentwicklung geeignet?

- ·Die besten MCUs/MPUs für industrielle humanoide Roboter