Flip-Flop vs. Latches: Hauptunterschiede zwischen ihnen

August 21 2023

Anfrage

Globaler Lieferant elektronischer Komponenten AMPHEO PTY LTD: Umfangreiches Inventar für One-Stop-Shopping. Einfache Anfragen, schnelle, individuelle Lösungen und Angebote.

SCHNELLE ANFRAGE

ZUR RFQ-LISTE HINZUFÜGEN

Flip-Flop ist synchron, Latches jedoch asynchron. Flip-Flops sind flankenempfindlich, Latches jedoch extrem empfindlich und verwenden ein Aktivierungssignal.

Was ist ein Flipflop?

Ein Flipflop ist eine grundlegende digitale Speicherschaltung, die ein Datenelement speichern kann. Eine Zeitschaltung verwendet ein Flipflop als Speicherkomponente. Ein Flipflop, eine Kombinationsschaltung oder beide Zeitschaltungen werden verwendet, um die Ausgabe zu erzeugen. Wenn der Taktimpuls im aktiven Zustand ist, wird der Zustand des Flipflops geändert; wenn er im inaktiven Zustand ist, bleibt er unverändert. Insbesondere verwenden synchrone Zeitschaltkreise nicht getaktete Flipflops als Speicherelemente, während asynchrone Zeitschaltkreise getaktete Flipflops als Speicherkomponenten verwenden.

Was ist ein Latch?

Ein Objekt zum Speichern eines Datenbits wird als Latch bezeichnet. Obwohl sie Flipflops ähneln, handelt es sich dabei nicht um synchrone Geräte. Sie arbeiten nicht an den äußeren Rändern der Uhr wie FFs. Ein Latch ist ein Gerät mit zwei stabilen Zuständen: hoher Ausgang und niedriger Ausgang. Der Latch kann die gespeicherten Daten sofort ändern, nachdem er für aktiviert erklärt wurde. Das Aktivierungssignal prüft den Eingang ständig, nachdem es aktiviert wurde. Diese Schaltkreise können in zwei Zuständen arbeiten, hoch und niedrig, abhängig vom aktivierten Signal.

Arten von Latches

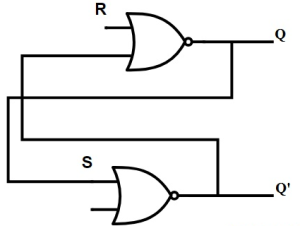

- SR-Latch

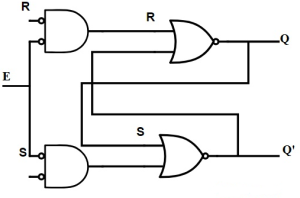

- Gated SR-Latch

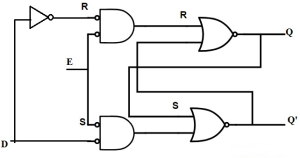

- D-Latch

- Gated D-Latch

- JK-Latch

- T-Latch

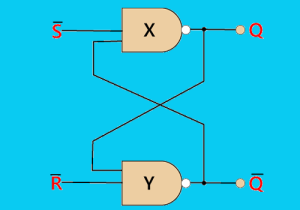

| SR Latch | |

|

| Ein asynchrones Gerät, bekannt als SR-Latches (Set/Reset) arbeiten unabhängig für Steuersignale, indem sie sich auf die S-Zustand- und R-Eingänge verlassen. Die beiden Eingänge werden ausgetauscht und gelöscht, wenn diese Latches mit NAND-Gattern aufgebaut sind. Daher wird es als SR'-Latch bezeichnet. |

| Gated SR Latch | |

|

| Ein Gated-SR-Latch ist alles, was eine unkomplizierte Erweiterung des SR-Latch ist. Bevor die Informationen zwischengespeichert werden, stellt es eine Aktivierungsleitung bereit, die hochgefahren werden muss. Der Ausgang kann sich sogar im mittleren Eingang des Freigabeimpulses ändern, obwohl die Steuerleitung erforderlich ist. Daher ist der Latch nicht synchron. |

| D-Latch | |

|

| Ein elektronischer Latch kann zum Speichern einzelner Daten verwendet werden. Wenn der Takteingang hoch ist, wird der D-Latch zum „Latchen“ oder Erfassen des Logikpegels verwendet, der auf der Datenleitung vorhanden ist. Wenn der Taktimpuls hoch ist und die Daten auf der D-Leitung ihren Zustand ändern, folgt der Ausgang Q dem Eingang D. |

| Gated D Latch | |

|

| Der Gated D Latch ist so ausgelegt, dass er nur den Gated SR Latch ändert, und die einzige Änderung am Gated SR Latch besteht darin, dass Eingang R so geändert werden muss, dass S invertiert wird. |

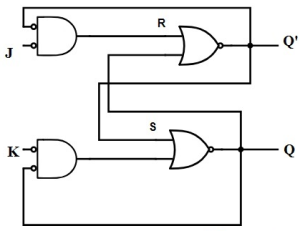

| JK Latch | |

|

| Der RS-Latch und der JK-Latch sind vergleichbar. Wie im Diagramm zu sehen ist, hat dieser Latch zwei Eingänge: J und K. Diese Form des Latchs beseitigt den verwirrenden Status an dieser Stelle. Der Ausgang wird geschaltet, wenn der JK-Latch-Eingang hoch ist. Die einzige Unterscheidung, die getroffen werden kann, ist die Ausgangsrückkopplung zum Eingang, die beim RS-Latch fehlt. |

| T-Latch | |

|

| Solange der JK-Latch-Eingang kurzgeschlossen ist, kann sich ein T-Latch bilden. Der T-Latch funktioniert auf diese Weise, wenn der Eingang des Latchs hoch ist, und der Ausgang wird dann umgeschaltet. |

Flipflop-Typen

- SR-Flipflop

- JK-Flipflop

- D-Flipflop

- T-Flipflop

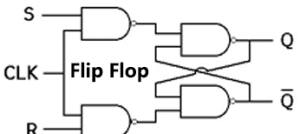

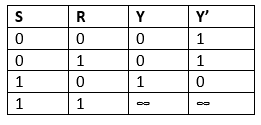

| SR-Flipflop | |

|

| Der in digitalen Systemen am häufigsten anzutreffende Flipfloptyp ist das SR-Flipflop. Bei einem SR-Flipflop ist der Ausgang Y hoch und Y' niedrig, wenn der gesetzte Eingang „S“ wahr ist. Die Beibehaltung der Schaltungsverdrahtung ist wichtig, nachdem die Ausgänge konstruiert wurden. Wir halten die Verdrahtung aufrecht, bis der Setz- oder Reset-Eingang hoch ist oder der Strom abgeschaltet wird. |

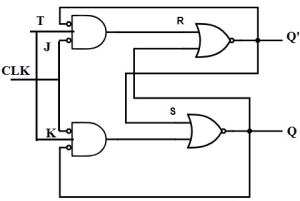

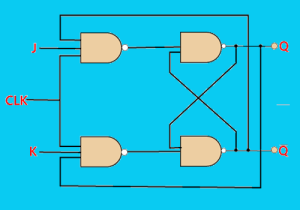

| JK Flip Flop | |

|

| Der Nachteil des SR-Flipflops, undefinierbare Zustände zu haben, wird durch das JK-Flipflop überwunden. Das JK-Flipflop wird durch Veränderung des SR-Flipflops hergestellt. Durch Verbesserung des SR-Flipflops wird das JK-Flipflop möglich. Wenn sowohl S- als auch R-Eingänge auf True gesetzt sind, macht das SR-Flipflop einen Fehler. Das JK-Flipflop liefert jedoch die gewünschten Ergebnisse. |

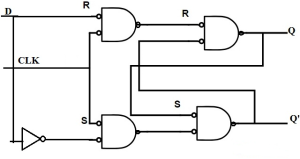

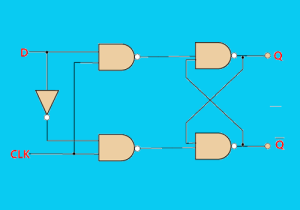

| D-Flipflop | |

|

| Das D-Typ-Flip-Flop behebt eines der Hauptprobleme der primären SR-NAND-Gatterschaltung, nämlich die Tatsache, dass es die Eingangszustände SET = "0" und RESET = "0" nicht zulässt. Dieser Zustand überschreibt den Rückkopplungs-Latch-Vorgang und zwingt beide Ausgänge auf logisch „1“, und der Eingang, der zuerst den Logikpegel „1“ erreicht, verliert die Kontrolle, während der Eingang, der noch auf logisch „0“ ist, den Endzustand des Latchs steuert. |

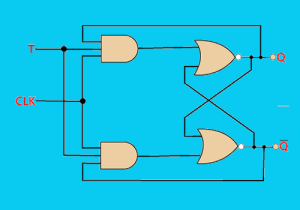

| T-Flip-Flop | |

|

| Es wird das T Flip Flop verwendet, das gleiche wie das JK Flip Flop. Im Gegensatz zu JK Flip Flops haben T Flip Flops nur einen Takteingang. Das T Flip Flop wird erzeugt, indem beide Eingänge des JK Flip Flops zu einer einzigen Information zusammengeführt werden. Das T Flip Flop wird auch als Toggle Flip Flop bezeichnet. Diese T Flip Flops können das Komplement ihres Zustands finden. |

Vor- und Nachteile von Flip-Flop und Latches

Vor- und Nachteile von Latches| Vorteile von Latches: |

| Die Form des Latches ist recht kompakt und nimmt weniger Platz ein. |

| Latch-basierte Schaltkreise nutzen geliehene Zeit, um Operationen abzuschließen, wenn sie nicht in einer vorgegebenen Zeitspanne abgeschlossen werden. |

| Verglichen mit Flip-Flop-Schaltkreisen bieten Latches eine aggressive Taktung. |

| Im Vergleich zu Flip-Flops ist das Latch-Design weitaus vielseitiger. |

| Latch-Geräte verbrauchen weniger Energie. |

| Da sie asynchron ausgelegt sind und kein CLK-Signal benötigen, ist die Latch-Leistung in Hochgeschwindigkeitsschaltungen schnell. |

| Nachteile von Latches: |

| Pegelsensitivität erschwert die Analyse der Schaltung. |

| Zum Testen der Schaltung kann eine zweite CAD-Anwendung verwendet werden. |

| Diese sind weniger wahrscheinlich, da die Wahrscheinlichkeit besteht, dass sie sich auf den Race Condition auswirken. |

| Es besteht die Möglichkeit einer Metastabilität, wenn ein Latch pegelsensitiv ist. empfindlich. |

Vor- und Nachteile von Flipflops

| Vorteile von Flipflops: |

| Um dies zu verhindern, ist es wichtig, Abschirmung und Filterung zu verwenden, um die Rauschmenge in einem System zu reduzieren. |

| Wenn ein System zu viel Rauschen ausgesetzt ist, kann ein Flipflop zufällig den Zustand wechseln, was zu einem Systemausfall führen kann. |

| Flipflops haben eine Reihe von Nachteilen, einer davon ist ihre Anfälligkeit für Rauschen. |

| Nachteile von Flipflops: |

| Mit Flip-Flops lassen sich komplexe Wellenformen erzeugen und sie können auch Zeitsignale liefern. |

| Um den Datenfluss in einem System zu steuern, können Flip-Flops auch zum Speichern von Daten in den Registern eines Systems verwendet werden. |

| Flip-Flops haben den großen Vorteil, dass sie Daten auch bei ausgeschalteter Stromversorgung speichern können. Sie können daher zum Speichern von Daten im Speicher verwendet werden. |

Flip-Flop vs. Latches-Anwendungen

Flip-Flop-Anwendungen

- Die Flip-Flop-Schaltung wird hauptsächlich im Speicher verwendet.

- Schalter zur Prellbeseitigung

- Register

- Zähler

- Frequenzteilung

- Datenspeicherung und -transport

Latches-Anwendungen

- Schaltungen wie Power-Gating und Uhren verwenden Latches als Speichermechanismus.

- D-Latches können mit Eingangs- oder Ausgangsports verwendet werden, die asynchrone Systeme sind.

- In synchronen Zweiphasensystemen werden Datenlatches verwendet, um die Transitanzahl zu senken.

- Latches werden typischerweise verwendet, um den Zustand der Bits beizubehalten, die zur Kodierung binärer Zahlen verwendet werden.

- Latches sind Einzelbit-Komponenten, die häufig in der Datenspeicherung und -berechnung verwendet werden.

Flip-Flop- vs. Latches-Schaltung und Wahrheitstabelle

| Flip-Flop-Schaltung | Flip-Flop-Wahrheitstabelle |

|

|

|

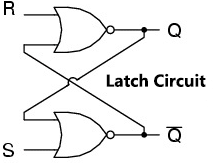

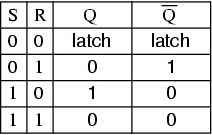

| Latches-Schaltung | Latches-Wahrheitstabelle |

|

|

|

Flip-Flop vs. Latches

| Latches | Flip-Flop |

| An den Taktdomänenübergängen in der Scan-Kette erfordert DFT Latches als Sperrzustand, um ein unberechenbares Verhalten zu verhindern. | Verwenden Sie scannbare Flops in DFT (steuerbar und beobachtbar). |

| Erhöhung der Menge an manuellen Berechnungen und Tool-Kontrolle, die erforderlich ist, um die Einhaltung der Zeit zu garantieren. | Die Überprüfung des Design-Timings ist einfach, wenn das statische Timing Es werden Tools für die Zyklusausleihe (STA) verwendet. |

| Zyklusausleihe, bei der davon ausgegangen wird, dass jede Schleife einen vollständigen Zyklus lang ausgeführt wird, erhöht die Einrichtungszeit für den folgenden Registerschritt. Zeitliche Fehlanpassungen werden von Designern berücksichtigt, die Latches als mögliche Lösung in Betracht ziehen. | Es startet an einer steigenden Flanke, daher müssen die Daten vor der nächsten steigenden Flanke eingerichtet werden. Wenn es zu spät ist, bricht das System zusammen. Selbst wenn es früh eintrifft, wird Zeit wegen der gezackten Kanten der Flops vergeudet. |

| Die hochempfindlichen Latches sind auf ein Aktivierungssignal angewiesen, um zu funktionieren. | Flip-Flops sind flankenempfindlich. |

| Bei ASICs mit starker Taktabweichung reduziert das Latching die Taktperiode erheblich. | Da sie nicht transparent sind, wird der Effekt der Taktabweichung selbst bei hochgeschwindigkeitsgepulsten Flip-Flops mit null Rüstzeit nicht verringert. |

| Sequentielle Schaltungsbausteine, sogenannte Latches, können mithilfe von Logikgattern hergestellt werden. | Flip-Flops sind ein gängiges Bauelement in sequentiellen Schaltungen, obwohl Latches auch verwendet werden können, um Flipflops. |

| Der Latch ist ein asynchroner Block. Daher ist es wichtig sicherzustellen, dass die kombinatorischen Funktionen, die die Eingangssignale an den Latch liefern, wettlauffrei sind. Andernfalls könnten sie Fehler erzeugen, die zum Latch führen und Ihr System gefährden könnten. | Flipflops hingegen erfahren nur dann Zustandsänderungen, wenn ein Steuersignal von hoch auf niedrig oder von niedrig auf hoch wechselt. |

| Der Pegel des Latchs, der ein binärer Eingang von entweder 1 oder 0 ist, beeinflusst sowohl den Ausgang des aktuellen Zustands als auch den Eingang des folgenden Zustands. | Wenn sich der Taktimpuls ändert, der entweder positiv (+ve) oder negativ (-ve) sein kann, ändern sich auch der nächste Zustandseingang und -ausgang eines Flipflops. |

Fazit zu Flip-Flop vs. Latches

Flip-Flop ist synchron, Latches jedoch asynchron. Flip-Flops sind flankenempfindlich, Latches jedoch extrem empfindlich und verwenden ein Aktivierungssignal. Ein Latch und ein Flip-Flop unterscheiden sich außerdem darin, dass ein Latch seinen Zustand ändern kann, wenn sich seine Eingänge ändern, während ein Flip-Flop dies nur tun kann, wenn sich ein Steuersignal von hoch auf niedrig oder von niedrig auf hoch ändert. Ein Latch wird pegelgesteuert ausgelöst, während ein Flip-Flop flankengesteuert wird. Latch-Überlegungen müssen ein ständiger Teil Ihres Designs sein.Verwandte Artikel

- ·Was sind die Hauptanwendungen von DSP in realen Szenarien?

- ·Was soll ich tun, wenn Arduino den seriellen Port nicht erkennt?

- ·Wie kann man einen Raspberry Pi für IoT-Projekte nutzen?

- ·Entwurf eines multifunktionalen Roboterarmsystems mit Gestenerkennungssteuerung auf Basis der FPGA-Technologie

- ·Abbauen Sie elektrisches Spielzeug für Mädchen, Der Verkäufer sagte, ich könnte es zur Arbeit tragen

- ·Entwurfstechniken zur Reduzierung des FPGA-Stromverbrauchs

- ·Bodenqualitätsüberwachungssystem basierend auf STM32-Mikrocontroller

- ·Honda Accord Auto Maschine demontiert, Werfen Sie einen Blick auf seine Verarbeitung und Materialien

- ·Was sind die am häufigsten verwendeten Sensoren in Embedded-Systemen?

- ·Wie implementiert man DSP (digitale Signalverarbeitung) auf einem Mikrocontroller (MCU)?

Populer Posts

Abbauen Sie elektrisches Spielzeug für Mädchen, Der Verkäufer sagte, ich könnte es zur Arbeit tragen

TMS320C6748BZWTD4E

Texas Instruments

ADSP-BF561SKBCZ-5A

Analog Devices Inc.

TMS320C6672ACYPA

Texas Instruments

ADSP-21060LCBZ-133

Analog Devices Inc.

TMS320DM8168BCYG0

Texas Instruments

SAF7771EL/200Z130K

NXP Semiconductors

MSC8156ETAG1000B

NXP Semiconductors

AD21478WYBCZ2A02

Analog Devices Inc.

TMS320C6713BPYP225

Ampleon USA Inc.

DM388AAAR21F

Texas Instruments

TMS320TCI6487FCUNA

Texas Instruments

AD21584WCBCZ4A12

Analog Devices Inc.