Taktmanagement in FPGAs/CPLDs

Globaler Lieferant elektronischer Komponenten AMPHEO PTY LTD: Umfangreiches Inventar für One-Stop-Shopping. Einfache Anfragen, schnelle, individuelle Lösungen und Angebote.

FPGAs/CPLDs Einführung

Von den vier Signalgruppen im digitalen Design - interne Signale, I/O-Signale, Reset und Takt - stellt letztere die höchsten Anforderungen an Signalqualität und Timing. Mängel im Taktnetzwerk können zu unerwünschtem, oft katastrophalem Verhalten der Schaltung führen. Um dies zu vermeiden, wurden spezielle Designregeln formuliert und Komponenten für die Taktverteilung in digitalen Schaltungen entwickelt. Die Methoden zur Signalführung in ASICs und FPGAs unterscheiden sich im Detail und unterscheiden sich auch von den Anforderungen und Methoden zur externen Signalführung auf Leiterplatten.

Grundlegende Anforderungen an Taktnetzwerke

Der Takt muss mit minimaler Verzerrung an alle getakteten Elemente (Flipflops, RAMs, I/O-Zellen) im IC (ASIC / FPGA) verteilt werden und in der Lage sein, eine sehr große Anzahl von Gate-Eingängen (bis zu mehreren Hunderttausend!) anzusteuern. Die Ausbreitungsverzögerung vom Chip-Eingang bis zu jedem Endpunkt des Netzwerks sollte idealerweise genau gleich sein. Dadurch wird sichergestellt, dass alle Flipflops ungefähr zur gleichen Zeit schalten, was eine hohe Synchronität garantiert. Die verbleibenden unvermeidbaren Unterschiede werden durch die Tools berücksichtigt, die ausreichende Zeitreserven bereitstellen. Der Unterschied in der Ausbreitungsverzögerung zwischen verschiedenen Endpunkten des Taktnetzwerks wird als Skew bezeichnet und liegt in modernen digitalen Schaltungen im Idealfall unter 100ps.

Um dies zu erreichen, werden eine Reihe von Maßnahmen ergriffen:

An den Eingängen von PLDs, FPGAs und ASICs sind spezielle Eingangspuffer vorgesehen, die teilweise von symmetrischen Signalquellen gespeist werden können.

In PLDs und FPGAs sind unterschiedliche Taktnetzwerke und Taktregionen vorgesehen. In ASICs werden diese nach Bedarf erstellt.

Es werden globale und teilweise auch regionale Takttreiber verwendet (in Xilinx-FPGAs: BUFG).

Taktnetzwerke werden oft als Baumstrukturen entworfen (d. h. mit gleicher Länge von der Baumwurzel bis zu jeder Astspitze). Diese Schaltungstechnik wird deshalb auch als „Clock Tree“ bezeichnet.

Clock Domains / Takterzeugung

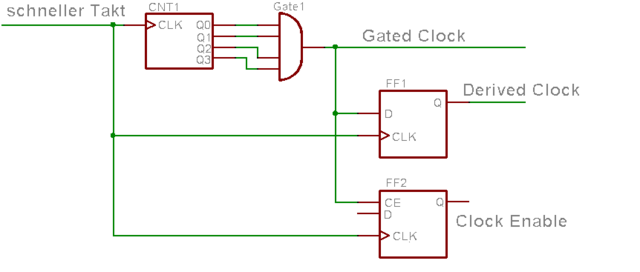

In fast jeder digitalen Schaltung sollen verschiedene Bereiche nicht bei jedem Taktzyklus eine Aktion ausführen oder mit einer deutlich geringeren Taktrate arbeiten als der Rest der Schaltung. Zu diesem Zweck muss aus dem relativ schnellen Systemtakt ein langsamer Takt abgeleitet werden. Was auf den ersten Blick einfach aussieht, wird im Detail oft falsch gemacht.

Gated Clocks

Hierunter versteht man geschaltete, also unterbrochene („gated“) Taktleitungen. Dies kann geschehen durch den Einsatz von:

- Multiplexern (Auswahl zwischen Taktquelle 1 und 2) oder

- Kombinatorischer Logik (Schaltungsteile werden unter bestimmten Bedingungen vom Takt getrennt)

Clock Enable

Jedes Flipflop in FPGAs/CPLDs besitzt einen synchronen Steuereingang namens CE (Clock Enable). Damit lässt sich festlegen, ob das Flipflop bei der nächsten Taktflanke neue Daten speichern oder die alten Daten behalten soll. Da es sich um einen synchronen Eingang handelt, ist es völlig unkritisch, wenn dieses Signal Störungen enthält.

Beispiele

Hier ist der optimierte VHDL-Code für die Verwendung von „Clock Enable“, der den Gewohnheiten eines englischsprachigen Publikums entspricht:

Bibliothek IEEE;

verwenden Sie IEEE.STD_LOGIC_1164.ALL;

verwenden Sie IEEE.NUMERIC_STD.ALL;

Entität clock_enable_example ist

Port (clk: in std_logic;

reset: in std_logic);

Ende clock_enable_example;

Architekturverhalten von clock_enable_example ist

Konstante CNT_DIV: Ganzzahl := 16; -- Taktteilungsverhältnis

Signal cnt: Ganzzahlbereich 0 bis CNT_DIV-1; -- Zähler für Taktteilung

Signal ce: std_logic;

begin

-- Prozess mit langsamer Taktfreigabe

process(clk)

begin

if rising_edge(clk) then

if ce = '1' then

-- Fügen Sie hier Aktionen ein, die mit der langsamen Uhr laufen

-- Beispiel: Geben Sie eine Meldung aus

report "Clock Enable is active!";

end if;

end if;

end process;

-- Generator für Taktfreigabe

process(clk)

begin

wenn steigende_Flanke(clk), dann

wenn zurücksetzen = „1“, dann

ce <= „0“;

cnt <= 0;

sonst

wenn cnt = CNT_DIV – 1, dann

ce <= „1“;

cnt <= 0;

sonst

ce <= '0';

cnt <= cnt + 1;

end if;

end if;

end if;

end process;

end Behavioral;

Signal- und Konstantendeklarationen:

CNT_DIV: Das Teilungsverhältnis für die Generierung des Taktfreigabesignals (ce). In diesem Beispiel wird das Taktfreigabesignal alle 16 Taktzyklen aktiviert.

cnt: Der Zähler, der zum Generieren des Taktfreigabesignals verwendet wird.

ce: Das Taktfreigabesignal.

Prozess für langsame Taktfreigabeaktionen:

Dieser Prozess wird an der steigenden Flanke des Eingangstakts (clk) ausgelöst.

Wenn das Taktfreigabesignal (ce) „1“ ist, werden die gewünschten Aktionen ausgeführt. Hier wird eine Beispielmeldung ausgegeben.

Clock Enable Generator:

Auch dieser Vorgang wird durch die steigende Flanke des Eingangstakts (clk) ausgelöst.

Der Zähler (cnt) erhöht sich mit jedem Taktzyklus, bis er den Wert CNT_DIV - 1 erreicht.

Wenn der Zähler CNT_DIV - 1 erreicht, wird das Taktfreigabesignal (ce) auf '1' gesetzt und der Zähler zurückgesetzt.

Andernfalls bleibt das Taktfreigabesignal (ce) auf '0' und der Zähler erhöht sich weiter.

Ein Rücksetzsignal (reset) wird hinzugefügt, um den Zähler und das Taktfreigabesignal bei Bedarf zu initialisieren.

Clock Skew

Mit der Einstellung Clock Skew wird eine Synthese Werkzeug kann angewiesen werden, das Timing der Taktflanke entsprechend den Anforderungen der Schaltungsverzögerungen anzupassen. Dadurch werden mehr Reserven geschaffen.

Phasenverschiebung

Innerhalb der FPGA-PLLs können mehrere Takte aus demselben Eingangstakt abgeleitet werden, die eine feste Verschiebung aufweisen. Diese Verschiebung ist das Hauptwerkzeug, um das erforderliche Timing für eine steigende Flanke eines internen Takts in Bezug auf extern eingehende Daten festzulegen und Ausbreitungsverzögerungen in den FPGA- und I/O-Bänken auszugleichen.